DOI: 10.15913/j.cnki.kjycx.2024.16.010

# 基于FPGA的角度编码器数据采集系统设计

刘塔拉,任同阳,于

(中国科学院长春光学精密机械与物理研究所, 吉林 长春 130033)

摘 要:为了实现高精度位置测量,设计了基于赛灵思公司Spartan6系列FPGA和海德汉公司RCN8510绝对式编码器的数 据采集系统。通过分析Endat数据协议,设计了信号采集电路硬件电路、功能模块和程序运行流程。采用线延迟补偿方法 和CRC校验设计,提高了系统的可靠性和数据检测速率。使用ChipScope软件检测FPGA内部信号,完成了设计功能的验 证。通过试验,验证了该系统满足3.125 MHz数据速率和10 kHz采样频率工作要求。

关键词:FPGA;绝对式角度编码器;Endat;CRC校验

中图分类号:TN762

文献标志码:A

文章编号:2095-6835(2024)16-0045-04

在伺服控制应用中,高精度位置测量是精密伺服 控制系统的关键点[1-2]。光电编码器作为高精度数字位 移传感器,目前被广泛应用在跟踪转台、数控机床和机 器人等领域[3]。海德汉公司的RCN8510绝对式角度编 码器常被应用于测量旋转轴位置系统,具有高精度和 高可靠性等优点。该编码器采用 Endat 通信协议, 随编 码器售卖的 Endat 接口数据采集电路价格非常昂贵。 FPGA 是现场可编程逻辑门阵列[4],可以通过 Verilog 硬 件描述语言编程芯片内部连线关系[5-6],实现设计功能。 通过自研基于 FPGA 的数据采集电路替代官方 Endat 采集设备,不仅可以节约成本,也可以根据项目需求定 制数据接口、采样频率和采样模式。

#### Endat协议 1

Endat 数据协议是用于编码器的双向数字接口,有 数据传输速度快和传输可靠性高等特点[7-8]。Endat数 据协议采用串行数据传输方式,物理接口需要1路供电 电源线和2对差分信号线[9-10]。数据传输保持与对接接 口电路时钟信号同步,可以传输位置值、参数和诊断信 息等数据类型,由对接电子电路发送的模式进行指令 控制。

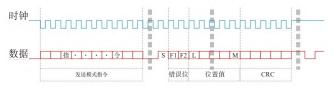

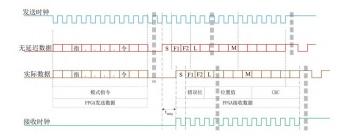

Endat协议时序图如图1所示。

图1 Endat协议时序图

在一个采集周期中,首先由控制电路发送同步时 钟和模式指令。当编码器成功计算出采样时刻位置值 后,由起始位S开始发送数据。后续是2个独立生成的 错误状态位 F1 和 F2, 是编码器自检结果, 报错意味着

编码器内部存在故障状态,导致无法正确计算数据。 之后编码器发送计算数据,发送顺序为由低到高。最 高位数据发送结束后接着发送5位循环冗余校验 (CRC)。数据传输完成后,需要将时钟线拉高一段时 间,完成一帧数据的采样。

# 2 系统硬件组成

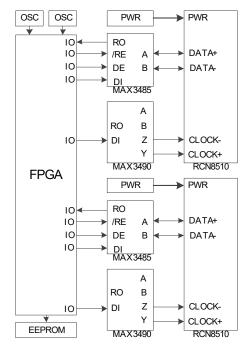

信号采集电路以FPGA作为核心芯片,由外围时 钟、电源、存储和接口芯片组成,硬件电路框图如图2 所示。

图2 系统硬件电路框图

FPGA采用 Xilinx 公司的 Spartan6 系列,该芯片有 9152个逻辑单元、102个用户IO,使用FPGA完成Endat 接口控制、数据采集和发送等工作。编码器的CLOCK 和DATA作为差分线路驱动器,是基于EIA RS485标准

的差分信号接口。本文利用通信接口芯片 MAX3485 和MAX3490芯片,完成FPGA的IO和编码器差分信号 之间的转换。MAX3485和MAX3490为RS485专用通 信接口芯片,最高转换速率达10 Mbps。其中MAX3490 具有全双工通信功能,FPGA给编码器提供的时钟信号 由FPGA IO发出,经MAX3490芯片DI脚输入,转化为 差分信号由 Z、Y 引脚输出。MAX3485 具有半双工通 信功能,通过DE和RE引脚控制芯片的收发方向。 FPGA 给编码器发送的控制指令由 FPGA IO 发出,经 MAX3485 芯片 DI 脚输入,转化为差分信号由A、B引 脚输出。由编码器返回FPGA的测量数据由差分信号 接口A、B引脚输入,转化为单端信号由RO引脚输出至 FPGA的IO。

本文中采用2套独立的编码器采集模块,通过 FPGA并行数据处理实现2个编码器独立并同步采集 和处理。

# 系统功能实现

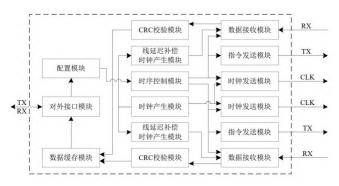

信号采集电路功能模块如图3所示,主要由时序控 制模块、时钟产生模块、时钟发送模块、指令发送模块、 数据接收模块、线延迟补偿时钟产生模块、CRC校验模 块、配置模块、数据缓存模块和对外接口模块组成。

图3 信号采集电路功能模块

时钟产生模块负责生成系统中使用的各种时钟信 号,包括Endat接口发送时钟、延迟补偿时钟、串行数据 接口时钟等。时序控制模块控制采样触发、数据线收 发切换、对外数据发送等时序。时钟发送模块负责向 编码器发送时钟信号CLK。指令发送模块负责发送 Endat 协议控制指令,之后由数据接收模块接收 Endat 接口返回的数据。线延迟补偿时钟产生模块根据时钟 产生模块和数据接收模块,产生与接收数据相位匹配 的时钟。CRC校验模块负责实时计算接收数据的CRC 校验结果,并检测CRC校验数据是否匹配。配置模块 主要控制数据速率、采样频率、控制指令和状态保存等 功能。数据缓存模块可以保存采样编码器数据和报错 状态等信息。对外接口模块主要负责接收上位机的控 制指令,并向上位机发送测量结果。

#### 3.1 Endat接口设计

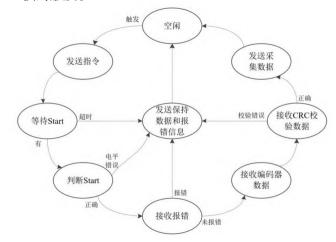

Endat接口程序执行逻辑如图 4 所示。在空闲状态 下等待采样触发信号,触发之后发送时钟和指令信号 并等待 Start 状态。接收到 Start 之后进行判断,判断 Start 正确后接收错误状态位1和错误状态位2。编码 器无报错状态下开始接收编码器数据和CRC校验。校 验通过后发送最新的采样数据,并回到空闲状态等待。 当出现 Start 等待时间超时、Start 位异常、编码器报错和 CRC校验未通过等状态时,会跳过正常程序循环,发送 保持数据和相对应的报错信息并回到空闲状态等待下 一帧的触发。

图 4 Endat接口程序执行逻辑

### 3.2 线延迟补偿设计

信号在电缆中传输及编码器内部信号传输导致传 输信号比理想情况延迟一定时间,延迟状态与编码器 本身和线缆长度有关。在高速信号传输时需要采用延 迟补偿方法保证接收数据功能。

线延迟补偿时序图如图5所示,在发送时钟和采集 编码器数据指令后,通过检测实际接收到的信号特征, 实时产生与之匹配的接收时钟。以接收时钟为基准, 采样接收信号电平,可以正确采集到数据。

图 5 线延迟补偿时序图

### 3.3 CRC校验设计

CRC检验数据用于检验传输链路中bit数据流是 否产生误码,从而确保传输数据的正确性[11-12]。CRC校 验是在传输数据后面加上相应位数的 CRC 校验码,接 收端收到数据后对数据和多项式所对应的数据进行 模2除法计算,若计算得到的校验数据与接收到的校验 数据一致,则证明传输数据无误码。RCN8510编码器 采用5位的CRC检验,其多项式为x<sup>5</sup>+x<sup>3</sup>+x+1,G(x) =6'b101011,单帧数据不可检测错误率为3.125%。

考虑到FPGA并行处理特性,在FPGA内部搭建组 合逻辑电路实现了CRC校验功能,数据接收完成时便 能计算出CRC校验结果,电路源码如下。其中d[30]至 d[0]分别为2 bit错误位和29 bit数据位。

$CRC[0] = d[30] \wedge d[25] \wedge d[24] \wedge d[23] \wedge d[21] \wedge d$ [20] ^ d[17] ^ d[15] ^ d[10] ^ d[9] ^ d[8] ^ d[6] ^ d[5] ^ d  $[2] ^ d[0];$

$CRC[1] = d[30] \wedge d[26] \wedge d[23] \wedge d[22] \wedge d[20] \wedge d$ [18] ^ d[17] ^ d[16] ^ d[15] ^ d[11] ^ d[8] ^ d[7] ^ d[5] ^  $d[3] \wedge d[2] \wedge d[1] \wedge d[0] \wedge 1;$

$CRC[2] = d[27] \wedge d[24] \wedge d[23] \wedge d[21] \wedge d[19] \wedge d$ [18] ^ d[17] ^ d[16] ^ d[12] ^ d[9] ^ d[8] ^ d[6] ^ d[4] ^ d  $[3] ^d[2] ^d[1];$

$CRC[3] = d[30] \wedge d[28] \wedge d[23] \wedge d[22] \wedge d[21] \wedge d$ [19] ^ d[18] ^ d[15] ^ d[13] ^ d[8] ^ d[7] ^ d[6] ^ d[4] ^ d [3] ^ d[0] ^ 1;

$CRC[4] = d[29] \wedge d[24] \wedge d[23] \wedge d[22] \wedge d[20] \wedge d$ [19] ^ d[16] ^ d[14] ^ d[9] ^ d[8] ^ d[7] ^ d[5] ^ d[4] ^ d[1];

## 实验验证

编码器数据采集卡设计了独立的2个编码器接口、 丰富的扩展IO和编码器码值指示灯及采集卡状态指 示灯。为了验证设计的电路和程序的功能,对本文中 设计的编码器信号采集系统进行上电测试。编码器采 用海德汉RCN8510绝对式圆光栅,采用Endat2.2协议, 数据输出为29 bit,测量精度达±1",单信号周期位置误 差小于等于±0.15″,总测量范围为0°~360°。

海德汉角度编码器数据采集系统实验如图6所示, 将设计完成的程序下载到FPGA板卡上,并将编码器 连接到数据采集卡的编码器接口1上。

(a)编码器数据采集卡

(b)编码器数据采集实验

图6 实验验证

利用 ISE 的信号捕捉软件 ChipScope 抓取 FPGA 内 部的信号进行分析,一帧采样信号如图7所示。

图7 chipscope 捕捉信号图

单帧的采样从外部触发信号trigger的上升沿开 始,当检测到触发信号时,开始生成编码器的时钟信号 clk,并将MAX3485芯片的输入输出方向信号dir拉高, 进入FPGA对编码器输出信号状态。经过10个周期 后,编码器控制指令信号由FPGA输出引脚tx IO发送 完成, MAX3485 芯片的输入输出方向信号 dir 拉低, 进 入 FPGA 接收编码器信号状态。经过一段时间的等待 后,FPGA接收信号电平拉高,由FPGA信号输入引脚 rx IO接收开始标志。随后rx IO接收的2个时钟的信 号为 err 错误状态,01表示编码器工作正常。检测编码 器报错信息之后由rx IO接收编码器采集并计算出 29位位置码。由于系统中CRC校验采用FPGA内部搭 建的数字电路生成,CRC校验计算结果crc calculate信 号从接收到第一个错误状态时就会随着接收数据寄存 器的变化而变化。当接收完成2 bit 错误位和29 bit 编 码器位置值,还未接收编码器的CRC校验数据时就已 经完成了计算。编码器位置值接收完成后由rx IO继 续接收编码器的CRC计算值。等待5个周期,完成 CRC校验值(1D)接收,校验码与FPGA内部的计算值 吻合,此时拉高check信号,标志着此帧信号校验正确。 一帧信号采集结束时,link信号拉高,表示整个信号采 集过程中信号特征正确,将接收到的编码器位置值锁 存到 data 寄存器并复位全部接口信号,完成一帧编码 器数据采集。

根据项目需求,本系统中采用了3.125 MHz频率 编码器时钟信号和10kHz编码器信号采样频率,将 RCN8510编码器连接到采集电路上,并通过示波器采 集了单帧信号波形和周期信号采集波形。

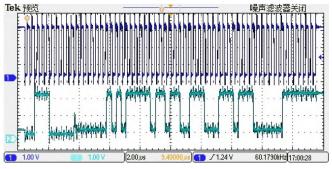

单帧信号波形图如图8所示。图8中信号1为发送 的时钟,信号2为数据信号。示波器x轴为时间轴,单 位为2 µs,y轴为信号幅值,单位为1 V。从波形图可以 看到时钟和数据均按设计运行,实现了3.125 MHz的 时钟和数据传输。

图8 单帧信号波形图

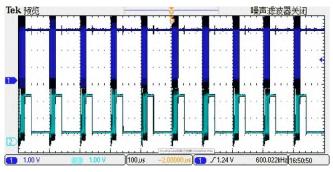

多帧信号波形图如图9所示。图9中信号1为发送 的时钟,信号2为数据信号,时间单位为100 μs。从波 形图可以看到2个采样帧间隔为100 μs,采样频率为 10 kHz

图 9 多帧信号波形图

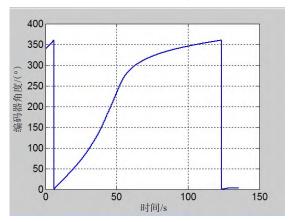

将编码器采集系统安装到设备中,在上位机接收 和记录编码器位置值,通过转动方位轴可以检测到角 度值从0°~360°循环。编码器角度值记录如图10所示。

图 10 编码器角度值记录

#### 5 结束语

本文根据项目需求,使用Endat协议的圆光栅绝对

式编码器 RCN8510 及自研基于 FPGA 的信号采集电 路,实现了高精度方位俯仰轴角度测量。根据 Endat 协 议完成了硬件电路设计、整体程序功能设计和Endat接 口设计。通过线延迟补偿实现了数据高速传输。采用 CRC校验算法,实现了数据误码检测。使用ChipScope 软件检测 FPGA 内部信号,完成了设计功能的验证。 实验结果表明,采样频率可达到10kHz,并可发送到后 续电子学设备中。

# 参考文献:

- [1] 张建辉,陈震林,张帆.绝对式光电编码器的编码理论研究 进展[J]. 振动测试与诊断,2021,41(1):1-12.

- [2] 邱靖超,刘新妹,殷俊龄,等.一种基于FPGA的步进电机控 制系统的设计[J]. 科技与创新,2021(8):11-14.

- [3] 赵长海,万秋华,梁立辉,等.小型高精度航天级光电编码 器[J]. 电子测量与仪器学报,2015,29(8):1224-1230.

- [4] 马彧.CPLD/FPGA可编程逻辑器件实用教程[M]. 北京:机 械工业出版社,2006.

- [5] 夏宇闻. Verilog 数字系统设计教程[M]. 3 版. 北京: 北京航空 航天大学出版社,2013.

- [6] 林灶生. Verilog FPGA芯片设计[M]. 北京:北京航空航天大 学出版社,2006.

- [7] 廖彩霞,赖欢,董佳.EnDat2.2通讯协议接口的设计[J].四川 兵工学报,2015,36(3):125-128.

- [8] 孙大海.基于FPGA和ARM设计EnDat2.2接口电路[D].长 春:中国科学院研究生院(长春光学精密机械与物理研究 所),2013.

- [9] JOHANNES H G. EnDat2.2-bidirectional interface for position encoders[R].2008.

- [10] 蔺春波,吴宏圣,乔栋,等.基于FPGA的EnDat协议时序研 究[J]. 电子测量技术,2016,39(3):91-94.

- [11] 左飞飞,杜英森,刘剑霏.基于递推法的CRC-32校验码并 行改进算法[J]. 探测与控制学报,2019,41(1):97-101.

- [12] 张树刚,张遂南,黄士坦.CRC校验码并行计算的FPGA实 现[J]. 计算机技术与发展,2007,17(2):56-58.

作者简介: 刘塔拉(1992-), 男, 蒙古族, 吉林长春人, 硕士,助理研究员,从事光电探测研究。

(编辑:严丽琴)