#### **PAPER**

# Silicon-on-silica waveguides-based all-optical logic gates at 1.55 $\mu \mathrm{m}$

To cite this article: Amer Kotb et al 2023 Phys. Scr. 98 035517

View the <u>article online</u> for updates and enhancements.

# You may also like

- A new scheme of all-optical 2:1 multiplexer (MUX) and MUX-based combinational circuits using nonlinear kerr-type materials Sourabh Kumar Das and Nirmalya Pahari

- Inverse design of ultra-compact photonic gates for all-optical logic operations

Berkay Neeli, Yusuf Abdulaziz Yilmaz, Hamza Kurt et al.

- Multifunctional optical logic device based on nanoscale rectangular ring resonator Junxiong Chai, Yiyuan Xie, Jing Tan et al.

# Physica Scripta

21 October 2022

REVISED 2 February 2023

ACCEPTED FOR PUBLICATION 10 February 2023

PUBLISHED

22 February 2023

#### **PAPER**

# Silicon-on-silica waveguides-based all-optical logic gates at $1.55 \, \mu \mathrm{m}$

Amer Kotb<sup>1,2,\*</sup>, Kyriakos E Zoiros<sup>3</sup> and Wei Li<sup>1,\*</sup>

- GPL Photonics Laboratory, State Key Laboratory of Luminescence and Applications, Changchun Institute of Optics, Fine Mechanics and Physics, Chinese Academy of Sciences, Changchun 130033, People's Republic of China

- Department of Physics, Faculty of Science, University of Fayoum, Fayoum 63514, Egypt

- Lightwave Communications Research Group, Department of Electrical and Computer Engineering, School of Engineering, Democritus University of Thrace, Xanthi 67100, Greece

- Authors to whom any correspondence should be addressed.

E-mail: amer@ciomp.ac.cn and weili1@ciomp.ac.cn

Keywords: logic gates, silicon-on-silica, contrast ratio

#### Abstract

The demand for faster and more efficient integrated photonic circuits has prompted the rise of siliconon-insulator technology. In this paper, silicon-on-silica waveguides have been employed for the alloptical realization of a complete family of logic gates, including XOR, AND, OR, NOT, NOR, NAND and XNOR operated at 1.55  $\mu$ m. This waveguide consists of three identical slots and six microring resonators, all made of silicon patterned on silica. The principle of operation of these logic gates is based on the constructive and destructive interference induced by the phase difference between the input signals. The gates' performance is evaluated against the contrast ratio (CR) metric. Compared to existing waveguides, the proposed waveguides achieve higher CRs with a speed as high as 120 Gb s<sup>-1</sup>.

#### 1. Introduction

All-optical logic gates (AOLGs) are essential elements for the optical processing of information, since they overcome the fundamental difficulties of their electronic counterparts, in particular the limited data transfer speed and bandwidth. These logic operations may serve as the basis for, or at least a component of, digital communication systems at THz frequencies as well as other complex photonic circuitry [1, 2]. Recently, silicon has been used as a basic element in making passive and active photonic devices owing to its high thermal and mechanical properties, stability, high quality, low loss and large bandwidth extending from 1.55  $\mu$ m to nearly 7  $\mu$ m [3]. On the other hand, owing to the high transparency of silicon in the infrared spectrum and the wide refractive index difference between silicon ( $\sim$  3.45) and silica ( $\sim$  1.46), silicon-on-insulator (SOI) waveguides exhibit unique optical features. With advancements in silicon electronic device fabrication, silicon photonic devices can now be made available by utilizing the same complementary metal-oxide-semiconductor (CMOS) platform [4], especially with the help of mature SOI technology. The development of the 6G and 7G communication era, which will enable real-time terabits per second wireless connectivity for network sensing, holographic communication, and the cognitive internet of everything, will be accelerated by the addition of silicon photonics to CMOS compatible terahertz technologies. In fact, silicon periodic waveguides [5], metal slot waveguides [6], metal-insulator-metal structures [7], gold nanowire waveguides [8], plasmonic nanoparticles [9], silicon hybrid waveguides [10], dielectric-metal-dielectric design [11], dielectric-loaded waveguides [12], photonic crystal waveguides [13], optical amplifiers [14], graphene plasmonic structures [15, 16] have all been reported to realize the AOLGs. Most of these designs have employed photonic crystals to implement one or at most two logic gates [5, 9, 10, 17–20], unlike our simple design, which implemented seven logic gates at once. And the other reported works have used noble metals such as gold and silver [6–9, 12], which are more expensive compared with the materials (i.e. silicon and silica) used in our design. Moreover, these reported schemes require complicated and extremely precise microfabrication technology. It is therefore still a significant challenge to realize multifunctional logic gates with high contrast ratios (CRs) between the output logic states '1'

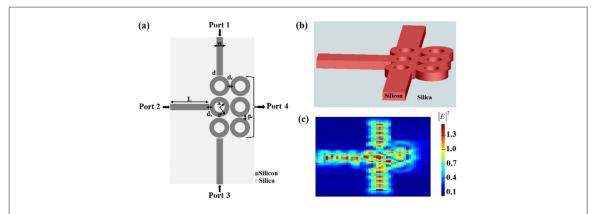

Figure 1. (a) Schematic diagram, (b) FDTD 3D view and (c) electric field intensity distributions of silicon-on-silica waveguide.

and '0' based on simple and less expensive waveguides. Additionally, the proposed design operates at a higher rate of 120 Gb s<sup>-1</sup> and achieves higher CRs than reported in previous designs [6, 7, 11–13]. This helps meet the growing demands and future needs for optical logic and processing at faster speeds and with better performance. Following these steps, in this research, we design seven basic logic operations, i.e. XOR, AND, OR, NOT, NOR, NAND and XNOR, using silicon-on-silica waveguides operated at 1.55  $\mu$ m. It is well known that silicon and silica exhibit negligible loss at shorter wavelengths, but at longer wavelengths, there are several multiphonon absorption peaks [21]. The proposed waveguide consists of three identical slots and six microring resonators. These logic operations are realized based on the constructive and destructive interferences between the input optical signals. With the convolutional perfectly matched layer (PML) as an absorbing boundary condition, a Lumerical finite-difference-time-domain (FDTD) simulation is run to simulate and demonstrate the operation of the proposed logic operations. The incident light will be absorbed with a minimum amount of reflections under the PML absorbing boundary conditions. However, spurious numerical reflections occur in a discretized FDTD space even when the PML is perfectly capable of absorbing incident beams. The coordinate stretching variables inside the PML might be graded to lessen these reflections [22]. The performance of these logic operations is evaluated against the contrast ratio (CR). According to the simulation results, the suggested compact waveguide can be used to realize AOLGs with higher CRs compared to previously reported structures [6, 7, 11-13].

#### 2. Silicon-on-silica waveguide

The suggested waveguide has a silicon core patterned on a silica substrate as cladding, which is beneficial for both linear and nonlinear applications as well as optical device size control [3]. There are three input ports, which are exposed to the transverse electric mode polarized wave, and one output port on this waveguide. When the incident light is passed through the inner microrings from the strips waveguide, the light builds up in intensity over multiple round-trips owing to constructive interference and is output to the three outer microrings which serve as the output port (i.e. port 4). The light traveling through the waveguides in the microrings remains within the waveguides due to the total internal reflection phenomena. Consequently, assuming there are no losses in the system such as those due to absorption, evanescence, or imperfect coupling, the intensity of the light emitted from the outer microrings will be equal to the intensity of the light fed into the waveguide.

High spectral transmission (T) is obtained if the microring resonators and the waveguide are brought close together, as in our case. Figure 1 shows the schematic diagram, FDTD 3D view and electric field intensity distributions of a silicon on-silica waveguide.

The intensity and wavelength of the input signals are identical. The FDTD tool's intensity monitors are adjusted to record the simulation results. To determine the appropriate logic function, the threshold transmission ( $T_{th}$ ) is first set to 0.26.  $T = I_{out}/I_{in}[12]$  is the spectral transmission, where  $I_{out} = |E_{out}|^2$  is the intensity at port 4 and  $I_{in} = I_1 + I_2 + I_3$  is the sum of the intensities at three input ports. When  $T > T_{th}$ , the logic output '1' is obtained; otherwise, the logic output is '0'. To optimize transmission, the incident beam must meet phase-matching conditions. When the incidence beams' phases are misaligned with the structure, destructive interference scatters the incident beams, resulting in a '0' output (i.e.  $T < T_{th}$ ). To assess the logic operations' performance, the CR is employed as the metric. It is defined as  $CR(dB) = 10 \ln[P_{mean}^1/P_{mean}^0][14]$ , where  $P_{mean}^1$  and  $P_{mean}^0$  are the mean peak powers of logical '1' and '0', respectively. The CR is commonly defined as in our case, i.e. by taking into account the power of all output logic bits, whereas other metrics such as the extinction ratio takes into account only the peak power of the minimum and the maximum output '1' and '0', respectively.

Thus, the CR provides a better and more accurate assessment of the performance of the all-optical logic gate scheme [23]. The wavelength of the microrings resonator ( $\lambda_s$ ) is defined as  $\lambda_s = 4\pi n_{eff} b$ , where  $n_{eff}$  is the effective refractive index and b is the radius of the outer microring [11]. All simulations were prepared and ran using FDTD with the default parameters listed in table 1.

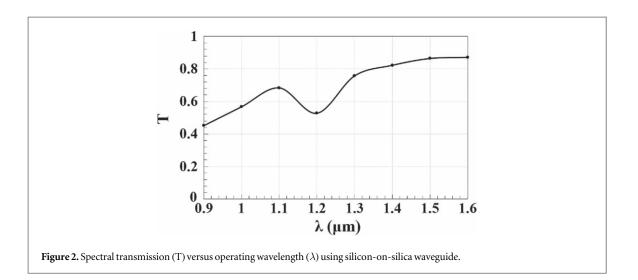

Figure 2 shows the spectral transmission (T) as a function of the operating wavelength ( $\lambda$ ) when the incident beams, as well as the Clk (all '1's), are launched at the three input ports with the same phase of 180°. This figure shows that the suggested waveguide achieves high T throughout a wide range of telecommunications wavelengths, from 1.3 to 1.6  $\mu$ m.

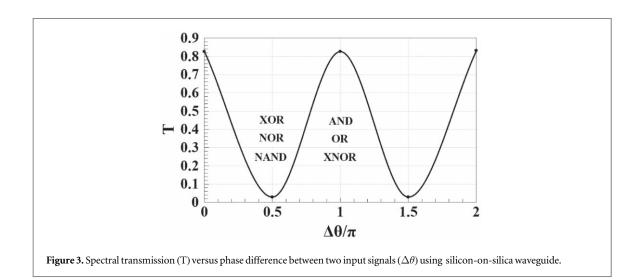

Figure 3 shows the variation in T of the proposed waveguide with the phase difference between the two input signals  $\Delta\theta = \theta_1 - \theta_2$  at 1.55  $\mu$ m operating wavelength. The minimum T = 0.029 and the maximum T = 0.831 correspond to  $\Delta\theta = (2n + 0.5)\pi$  and  $\Delta\theta = 2n\pi$  [12], where n = 0, 1, 2,..... Thus, this figure indicates that different optical logic functions can be realized at different values of  $\Delta\theta$ .

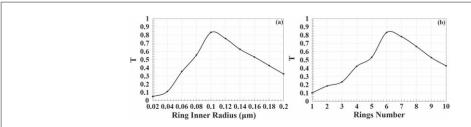

For more realistic results, we have tested the design performance using different rings number of different sizes. Therefore, we optimized the size and number of rings to avoid unintended crosstalk and hence realize the considered gates with higher CRs. Figure 4 shows the dependence of the T on the ring's inner radius and rings number. It is clear from these figures that in order to achieve the proposed gates with high CRs, each slot must be assigned an inner and an outer microring with an inner radius of  $0.1~\mu m$ . Accordingly, by decreasing the number of rings to less than six or increasing them to more than six, high optical losses are incurred as a direct by-product of the light scattering and absorption within the materials, which in turn reduces the CR.

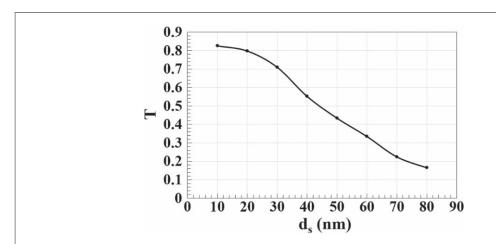

The distance between the strip and inner microring ( $d_s$ ) plays an important role in the proposed design in order to implement the considered logic gates with high CRs. Thus, the simulated spectral transmission (T) as a function of  $d_s$  at 1.55  $\mu$ m is shown in figure 5. This figure shows that the silicon-on-silica waveguide achieves high T = 0.552 up to  $d_s$  = 40 nm. This outcome demonstrates that the suggested design could be implemented in

Figure 4. Spectral transmission (T) versus (a) ring inner radius and (b) rings number using silicon-on-silica waveguide at 1.55  $\mu$ m.

Figure 5. Spectral transmission (T) versus distance between strip and inner microring ( $d_s$ ) using silicon-on-silica waveguide at 1.55  $\mu$ m.

| Table 1. | Simulation parameters. |

|----------|------------------------|

|----------|------------------------|

| Symbol    | Definition                                 | Value | Unit             |

|-----------|--------------------------------------------|-------|------------------|

| L         | Length of stripe                           | 1.0   | $\mu$ m          |

| w         | Width of stripe                            | 0.3   | $\mu$ m          |

| d         | Thickness of stripe                        | 0.3   | $\mu$ m          |

| a         | Inner radius of microring                  | 0.1   | $\mu$ m          |

| b         | Outer radius of microring                  | 0.22  | $\mu$ m          |

| $d_s$     | Distance between strip and inner microring | 0.01  | $\mu \mathrm{m}$ |

| Dr        | Distance between microrings                | 0.01  | $\mu$ m          |

| $\lambda$ | Operating wavelength                       | 1.55  | $\mu$ m          |

| $T_{th}$  | Threshold transmission                     | 0.26  | _                |

practice and transformed into a working prototype based on the specified design with the development of nanofabrication techniques in recent years, such as lithographic fabrication methods [8] and femtosecond laser direct writing technology [24–28].

# 3. Logic gates

#### 3.1. XOR

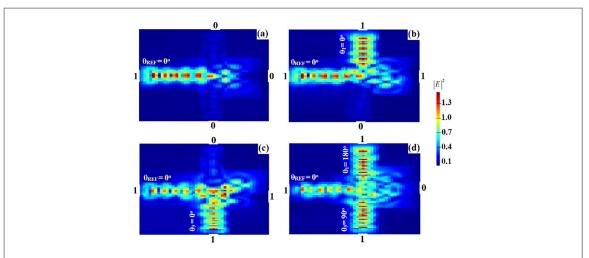

A reference beam (REF) must be injected into port 2 of figure 1, and the other two beams must be launched from ports 1 and 3 in order to construct the XOR, AND, and OR logic gates. The REF, which is a series of consecutive '1', i.e. all '1's, is used here to create a reference phase difference between input signals, thereby causing constructive or destructive interference. When two input signals are '0' and '1', or vice versa (i.e. 01 or 10) and REF (all '1's) are all adjusted with the same phase of  $0^{\circ}$ , port 4 generates logical '1' due to the constructive interference between the input beams. When both ports 1 and 3 are '1' at  $\theta_1 = 180^{\circ} \& \theta_3 = 90^{\circ}$  launched with

**Figure 6.** XOR field intensity distributions using silicon-on-silica waveguide at 1.55  $\mu$ m. (a) '00' input, (b) '01' input, (c) '10' input and (d) '11' input.

**Figure 7.** AND field intensity distributions using silicon-on-silica waveguide at 1.55  $\mu$ m. (a) '00' input, (b) '01' input, (c) '10' input and (d) '11' input.

**Table 2.** XOR simulation results ( $T_{th} = 0.26$ ).

| Port 1 | Port 3 | Port 2 (REF) | T     | Port 4 | CR (dB) |

|--------|--------|--------------|-------|--------|---------|

| 0      | 0      | 1            | 0.029 | 0      | 23.62   |

| 0      | 1      | 1            | 0.524 | 1      |         |

| 1      | 0      | 1            | 0.452 | 1      |         |

| 1      | 1      | 1            | 0.063 | 0      |         |

REF at  $\theta_{\rm REF} = 0^{\circ}$ , the output of port 4 produces '0' because of destructive interference between the input signals. The XOR gate is then achieved between the two input beams. Figure 6 illustrates the field intensity distributions for the logic XOR gate at 1.55  $\mu$ m.

Due to the relatively slight difference between the mean peak powers of '1' and '0', a CR = 23.62 dB is obtained. The XOR simulation results are listed in table 2.

#### 3.2. AND

The AND operation is performed by inserting two signals into ports 1 and 3, as well as the REF (all '1's) into port 2 (see figure 1). The phase angle of REF is adjusted at  $\theta_{REF} = 0^{\circ}$ . When two signals '1' and '0', or vice versa (i.e. 01 or 10), are injected at a different phase than the REF phase, destructive interference occurs due to the phase difference between the input beams, resulting in '0' output. When both input signals are '1', port 4 provides '1'

**Figure 8.** OR field intensity distributions using silicon-on-silica waveguide at 1.55  $\mu$ m. (a) '00' input, (b) '01' input, (c) '10' input and (d) '11' input.

**Table 3.** AND simulation results ( $T_{th} = 0.26$ ).

| Port 1 | Port 3 | Port 2 (REF) | T     | Port 4 | CR (dB) |

|--------|--------|--------------|-------|--------|---------|

| 0      | 0      | 1            | 0.029 | 0      | 26.40   |

| 0      | 1      | 1            | 0.075 | 0      |         |

| 1      | 0      | 1            | 0.073 | 0      |         |

| 1      | 1      | 1            | 0.826 | 1      |         |

**Table 4.** OR simulation results ( $T_{th} = 0.26$ ).

| Port 3 | Port 2 (REF)    | T                                    | Port 4                              | CR (dB)                                   |

|--------|-----------------|--------------------------------------|-------------------------------------|-------------------------------------------|

| 0      | 1               | 0.029                                | 0                                   | 30.33                                     |

| 1      | 1               | 0.524                                | 1                                   |                                           |

| 0      | 1               | 0.452                                | 1                                   |                                           |

| 1      | 1               | 0.831                                | 1                                   |                                           |

|        | Port 3  0 1 0 1 | Port 3 Port 2 (REF)  0 1 1 1 0 1 1 1 | 0 1 0.029<br>1 1 0.524<br>0 1 0.452 | 0 1 0.029 0<br>1 1 0.524 1<br>0 1 0.452 1 |

output owing to constructive interference, which occurs because the input signals and Clk have the same phase, i.e.  $\theta_1 = \theta_3 = \theta_{REF} = 0^\circ$ . As a result, the AND logic operation is functionally achieved. The field intensity distributions for the logic AND gate at 1.55  $\mu$ m can be seen in figure 7.

The AND simulation results with  $CR = 26.40 \, dB$  are summarized in table 3.

# 3.3. OR

In this case, two beams are supplied into the waveguide from ports 1 and 3, respectively, while the REF is supplied from port 2 (see figure 1). When only one of the OR gate's inputs is '1', the outcome is '1'. Therefore, this gate can be straightforwardly realized when all input beams propagate at the same phase, i.e.  $\theta_1 = \theta_3 = \theta_{REF} = 0^{\circ}$ , resulting in '1' output due to constructive interference between the input beams. Figure 8 depicts the field intensity distributions for the logic OR gate using the proposed waveguide at 1.55  $\mu$ m.

Table 4 displays the simulation results for the OR gate at 1.55  $\mu$ m with respect to T and CR. The huge difference between the mean peak powers of logical '1' and '0' allows for a high CR = 30.33 dB.

# 3.4. NOT

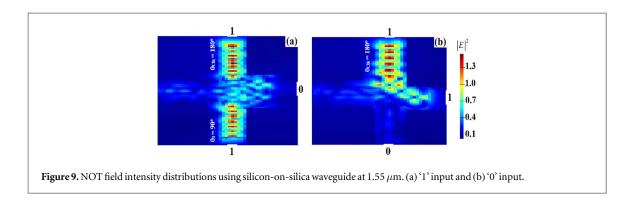

The proposed waveguide must receive a clock light (Clk) with an angle of  $180^\circ$  degrees from port 1 in order to operate all inverted logic gates, including NOT, NOR, NAND, and XNOR. The Clk introduces an additional phase shift on the traveling beams, which changes the waveguide balance and results in an output. The Clk input is a series of consecutive 1', i.e. all '1's. To implement the NOT logic gate, one beam is fed into port 3 at an angle of  $90^\circ$ . When port 3 is set to '1', the input beams experience different phases, causing destructive interference, resulting in a logical '0' output (i.e.  $T < T_{th}$ ). When port 3 is '0', the Clk does not experience any differencing

**Table 5.** NOT simulation results ( $T_{th} = 0.26$ ).

| Port 1 (Clk) | Port 3 | T     | Port 4 | CR (dB) |

|--------------|--------|-------|--------|---------|

| 1            | 1      | 0.062 | 0      | 20.51   |

| 1            | 0      | 0.482 | 1      |         |

phase, resulting in logical '1' output (i.e.  $T > T_{th}$ ) at port 4. In this way, the NOT gate is implemented. Figure 9 shows the field intensity distributions for the NOT gate at 1.55  $\mu$ m.

Table 5 summarizes the simulation results of the NOT function. These results show that the proposed waveguide can be used to form a NOT logic gate at 1.55  $\mu$ m with CR = 20.51 dB.

#### 3.5. NOR

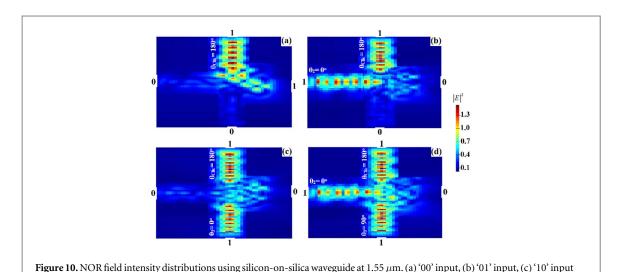

and (d) '11' input.

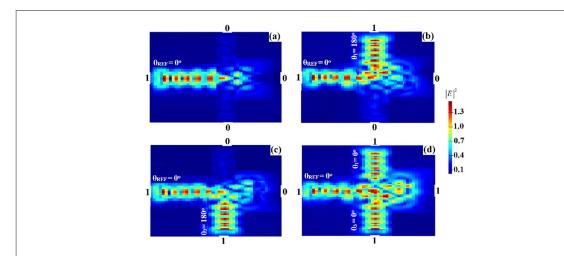

The NOR gate produces an output '1' if and only if all inputs are '1'. In order to realize the NOR gate, the Clk is injected into port 1, while the two other beams are injected into ports 2 and 3, respectively (see figure 1). The phase angle of Clk is first set at  $\theta_{\rm Clk}=180^\circ$ . The input beams' combination (01, 10, or 11) is injected at different angles, resulting in logical '0' at port 4 due to destructive interference. If the beams' combination (00) is launched, the Clk beam having  $\theta_{\rm Clk}=180^\circ$  will cancel the phase balance of the three ports, resulting in a logical '1' at port 4. The Boolean NOR logic gate is thus realized, as illustrated in figure 10.

The simulation results for the NOR gate with  $CR = 23.50 \, dB$  are summarized in table 6.

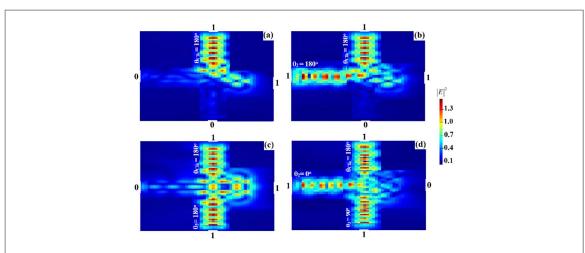

#### 3.6. NAND

NAND gate (NOT-AND) produces '0' output if and only if all its inputs are '1'. The NAND gate can be realized by injecting the Clk into port 1 and the two other beams into ports 2 and 3, respectively. When ports 2 and 3 are 'OFF' (i.e. 00), the output is '1' due to the Clk having  $\theta_{\text{Clk}} = 180^{\circ}$ . In this case, the T value is slightly above the T<sub>th</sub>. When (01, 10) are launched with Clk at the same angle of 180°, constructive interference is simply happening,

**Figure 11.** NAND field intensity distributions using silicon-on-silica waveguide at 1.55  $\mu$ m. (a) '00' input, (b) '01' input, (c) '10' input and (d) '11' input.

**Table 6.** NOR simulation results ( $T_{th} = 0.26$ ).

| Port 1 (Clk) | Port 2 | Port 3 | T     | Port 4 | CR (dB) |

|--------------|--------|--------|-------|--------|---------|

| 1            | 0      | 0      | 0.482 | 1      | 23.50   |

| 1            | 0      | 1      | 0.061 | 0      |         |

| 1            | 1      | 0      | 0.042 | 0      |         |

| 1            | 1      | 1      | 0.035 | 0      |         |

|              |        |        |       |        |         |

**Table 7.** NAND simulation results ( $T_{th} = 0.26$ ).

| Port 1 (Clk) | Port 2 | Port 3 | T     | Port 4 | CR (dB) |

|--------------|--------|--------|-------|--------|---------|

| 1            | 0      | 0      | 0.482 | 1      | 29.14   |

| 1            | 0      | 1      | 0.832 | 1      |         |

| 1            | 1      | 0      | 0.452 | 1      |         |

| 1            | 1      | 1      | 0.032 | 0      |         |

|              |        |        |       |        |         |

resulting in '1' output. Whereas a destructive interference results in '0' output when (11) is launched with Clk at different phases, i.e.  $\theta_2 = 0^\circ$ ,  $\theta_3 = 90^\circ$  and  $\theta_{Clk} = 180^\circ$ , as shown in figure 11.

Table 7 summarizes the simulation results for the NAND gate. When employing the proposed waveguide at 1.55  $\mu$ m, the mean peak power of '1' is larger than that of '0', resulting in a high CR = 29.14 dB for the NAND function.

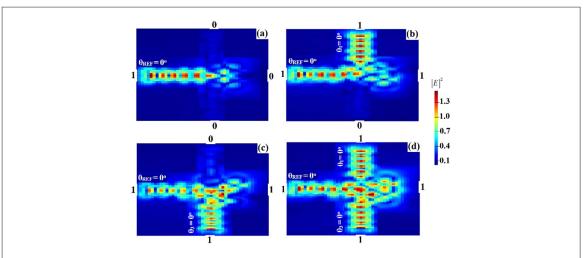

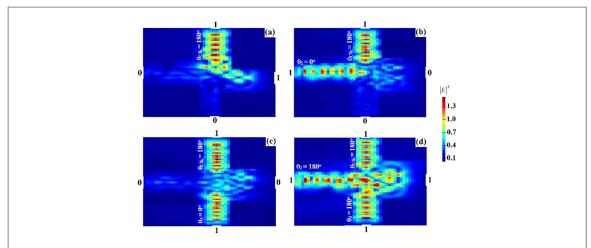

# **3.7. XNOR**

Similar to the NOR and NAND gates, the Clk enters port 1, while the two other beams are injected from ports 2 and 3, respectively. The output port 4 generates a '1' due to constructive interference when the input beams' combination (11) is inserted along with the Clk at the same phase. For (00) combination, the Clk at 180° results in '1' output. By contrast, port 4 produces a '0' when the signals' combination (01) or (10) is launched with a different phase, as shown in figure 12.

The XNOR gate has a high CR = 25.46 dB due to the large difference in the mean peak powers of the '1' and '0' bits. Table 8 summarizes the XNOR simulation results.

The Nyquist formula, which uses the terms B for the optical bandwidth and M for the total number of signal levels, calculates the speed of a transmission system as  $B \log_2[M]$  [29]. B is defined as  $B = (c/\lambda^2)\Delta\lambda$ , where c is the speed of light in a vacuum,  $\lambda = 1.55~\mu m$  is the wavelength of the optical carrier and  $\Delta\lambda$  is the spectral width of the signal. This indicates that the projected speed in our scenario, where B = 30~GHz and for four signal levels (00, 01, 10, 11), is  $120~Gb~s^{-1}$ .

Silicon and silica are common in the Earth's crust and are important components of the Earth's mantle. Therefore, the experimental verification of the proposed waveguide can be done based on the main outcomes of this simulation, given that the required technology is accessible. This is a technology issue that can be addressed

Figure 12. XNOR field intensity distributions using silicon-on-silica waveguide at 1.55  $\mu$ m. (a) '00' input, (b) '01' input, (c) '10' input and (d) '11' input.

**Table 8.** XNOR simulation results ( $T_{th} = 0.26$ ).

| Port 1 (Clk) | Port 2 | Port 3 | T     | Port 4 | CR (dB) |

|--------------|--------|--------|-------|--------|---------|

| 1            | 0      | 0      | 0.482 | 1      | 25.46   |

| 1            | 0      | 1      | 0.061 | 0      |         |

| 1            | 1      | 0      | 0.042 | 0      |         |

| 1            | 1      | 1      | 0.832 | 1      |         |

|              |        |        |       |        |         |

Table 9. Comparison of our and various reported waveguide-based designs of AOLGs at different wavelengths.

| Operations                         | Design                             | wavelength (nm) | CR (dB)     | References |

|------------------------------------|------------------------------------|-----------------|-------------|------------|

| NOT, XOR, AND, OR, NOR, NAND, XNOR | Metal slot waveguide               | 632.8           | 6–16        | [6]        |

| NOT, XOR, AND, OR, NOR, NAND, XNOR | Metal-insulator-metal structures   | 632.8           | 15          | [7]        |

| NOT, XOR, AND, OR, NOR, NAND, XNOR | Dielectric-metal-dielectric design | 900 and 1330    | 5.37-22     | [11]       |

| XOR, AND, OR, NOR, NAND, XNOR      | Dielectric-loaded waveguides       | 471             | 24.41-33.39 | [12]       |

| AND, XOR, OR, NOT, NAND, NOR XNOR  | Photonic crystal waveguides        | 1550            | 5.42-9.59   | [13]       |

| XOR, AND, OR, NOT, NOR, NAND, XNOR | Silicon-on-silica waveguides       | 1550            | 20.51-30.33 | This work  |

in practice, rather than a fundamental impediment. Design and fabrication of SOI microring resonators and slots waveguides have been experimentally reported for AOLGs [6, 8, 30–32].

Table 9 compares the proposed waveguide to various reported designs for the realization of AOLGs at different wavelengths. The suggested waveguides have higher CRs, while they are made of less expensive materials compared to other reported designs.

The proposed waveguide is more scalable, as it is simple to use to implement more combinational logic circuits such as adders and latches. Besides, the operating wavelengths can be turned on or off on demand, which allows for the easy provisioning of services and quick scaling for a growing network. The proposed waveguide is also small and light. It can typically be placed in optical computers for growth needs up to 15 to 20 years in the future. Furthermore, additional optical components can be installed later to make way for network expansion. However, the optical losses limit the scalability [33]. Thus, the losses must be minimized at the coupling interfaces between the strips and microrings by optimizing the waveguide operational parameters as in our case. The overall loss is very low (i.e. ~1.8 dB) thanks to the high spectral T that our compact waveguide emits.

# 4. Conclusion

Using a compact silicon-on-silica waveguide, we realized a complete family of basic Boolean operations operated at 1.55  $\mu$ m. These operations were simulated using the FDTD method. The micro-waveguide consists of three identical slots and six ring resonators. The constructive and destructive interferences induced by the

**IOP** Publishing Phys. Scr. **98** (2023) 035517 A Kotb et al

phase difference of the input signals form the basis for the proper operation of these logic gates. The suggested waveguide produces higher contrast ratio values than previously reported.

# Acknowledgments

Amer Kotb acknowledges the President's International Fellowship Initiative of the Chinese Academy of Sciences (Grant code: 2022VMB0013) for support this work.

# Data availability statement

The data cannot be made publicly available upon publication because they are not available in a format that is sufficiently accessible or reusable by other researchers. The data that support the findings of this study are available upon reasonable request from the authors.

#### **ORCID** iDs

```

Amer Kotb  https://orcid.org/0000-0002-3776-822X Wei Li  https://orcid.org/0000-0002-2227-9431

```

# References

```

[1] Ortiz-Martinez M, Hernandez-Serrano A I, Justo Guerrero M A, Strupiechonski E and Castro-Camus E 2020 J. Opt. Soc. Am. B 37

[2] Manjappa M, Pitchappa P, Singh N, Wang N, Zheludev N I, Lee C and Singh R 2018 Nat. Commun. 9 4056

[3] Tong X C 2014 Springer Series in Advanced Microelectronics 46 253-87

[4] Liu S, Norman J, Dumont M, Jung D, Torres A, Gossard A C and Bowers J E 2019 ACS Photon. 6 2523-9

[5] Zeng S, Zhang Y and Pun E 2010 Photon. Nanostr. Fundam. Appl. 8 32

[6] Pan D, Wei H and Xu H 2013 Opt. Express 21 9556

[7] Bian Y and Gong Q 2014 Opt. Commun. 313 27-35

[8] Gao L, Chen L, Wei H and Xu H 2018 Nanoscale 10 14771

[9] Nozhat N, Alikomak H and Khodadadi M 2017 Opt. Commun. 392 208-13

[10] Cui L and Yu L 2018 Mod. Phys. Lett. B 32 1850008

[11] Al-Musawi H K, Al-Janabi A K, Al-Abassi S A W, Abusiba N A A and Al-Fatlawi N A Q 2020 Optik 223 165416

[12] Yao C, Kotb A, Wang B, Singh S and Guo C 2020 Opt. Lett. 45 3769–72

[13] Rani P, Kalra Y and Sinha R K 2015 Optik 126 950-5

[14] Kotb A and Guo C 2021 Opt. Laser Technol. 137 106828

[15] Keshtkar P, Miri M and Yasrebi N 2021 Appl. Opt. 60 7234-42

[16] Khodadadi M, Moshiri S M M and Nozhat N 2020 IEEE Sensors J. 20 9114-23

[17] Ishizaka Y, Kawaguchi Y, Saitoh K and Koshiba M 2011 Opt. Commun. 284 3528-33

[18] Husko C, Vo T D, Corcoran B, Li J, Krauss T and Eggleton B 2011 Opt. Express 19 20681-90

[19] Andalib P and Granpayeh N 2009 J. Opt. Soc. Am. B 26 10-6

[20] Jandieri V, Khomeriki R and Erni D 2018 Opt. Express 26 19845-53

[21] Mashanovich GZ, Milošević MM, Nedeljkovic M, Owens N, Xiong B, Teo EJ and Hu Y 2011 Opt. Express 197112-9

[22] Laakso I, Ilvonen S and Uusitupa T 2007 Phys. Med. Biol. 52 7183-92

[23] Zoiros K E, Papadopoulos G, Houbavlis T and Kanellos G T 2006 Opt. Commun. 258 114-34

[24] Li M et al 2022 Photon. Res. 10 1533-42

[25] Zhang Q, Li M, Xu J, Lin Z, Yu H, Wang M, Fang Z, Cheng Y, Gong Q and Li Y 2019 Photon. Res. 7503-7

[26] Atzeni S, Rab A S, Corrielli G, Polino E, Valeri M, Mataloni P, Spagnolo N, Crespi A, Sciarrino F and Osellame R 2018 Optica 5 311-4

[27] Wei D et al 2018 Nat. Photon. 12 596-600

[28] Marshall G D, Politi A, Matthews J C F, Dekker P, Ams M, Withford M J and O'Brien J L 2009 Opt. Express 17 12546-54

[29] Crisp J and Elliott B 2005 Introduction to Fiber Optics 3rd ed. (Amsterdam: Elsevier)

[30] Donzella V, Sherwali A, Flueckiger J, Grist SM, Fard ST and Chrostowski L 2015 Opt. Express 23 4791–803

[31] Fu Y, Hu X, Lu C, Yue S, Yang H and Gong Q 2012 Nano Lett. 12 5784-90

[32] Kita S, Nozaki K, Takata K, Shinya A and Notomi M 2020 Commun. Phys. 3 33

[33] Monroy I T and Tangdiongga E 2007 Crosstalk in WDM Communication Networks (Germany: Springer)

```