# All-optical logic operations based on silicon-on-insulator waveguides

# Amer Kotboa,b,\* and Chaonan Yaooc

<sup>a</sup>Chinese Academy of Sciences, Changchun Institute of Optics, Fine Mechanics and Physics, GPL Photonics Laboratory, State Key Laboratory of Luminescence and Applications, Changchun, China

<sup>b</sup>University of Fayoum, Department of Physics, Faculty of Science, Fayoum, Egypt <sup>c</sup>Hisense Broadband Multimedia Technologies Co., Ltd., Qingdao, China

**Abstract.** Silicon waveguides are particularly appealing for the implementation of all-optical (AO) signal processing devices and switches due to the improved fabrication technology of silicon. Therefore, a silicon-on-silica waveguide is employed as the building block for simulating fundamental AO logic operations, including XOR, AND, OR, NOT, NOR, NAND, and XNOR, at 1.33-μm telecommunications wavelength. The proposed waveguide consists of two microring resonators and three strip waveguides. The operation concept of these logic gates relies on the constructive and destructive interference that results from the phase difference induced by incident optical beams. The performance of the target logic gates is assessed against the contrast ratio (CR) metric. The simulation results suggest that, by exploiting the proposed waveguides, these gates can operate with higher CR and faster speed compared to other designs. © 2023 Society of Photo-Optical Instrumentation Engineers (SPIE) [DOI: 10.1117/1.OE.62.4.048101]

**Keywords:** optical logic operations; silicon-on-insulator waveguide; contrast ratio.

Paper 20230011G received Jan. 5, 2023; accepted for publication Mar. 23, 2023; published online Apr. 5, 2023.

#### 1 Introduction

Silicon (Si) is too reactive to be found in nature, but it's found in practically all rocks as well as sand, clays, and soils, combined with oxygen as silicon dioxide (silica, SiO<sub>2</sub>). Si is produced commercially by the reduction of SiO<sub>2</sub> with coke in an electric furnace. SiO<sub>2</sub>, on the other hand, is the most abundant mineral found in the crust of the earth. Si possesses a high optical damage threshold, high quality and stable oxide, low-loss, and significant third-order optical nonlinearities, all of which are important qualities in photonics devices. With fully compatible production techniques, silicon-on-insulator (SOI) material has recently become a prominent platform for both photonic and electronic devices such as modulators, photodetectors, couplers, switches, T- and Y-branches, and gratings. On the other hand, the development of all-optical (AO) logic technologies is fundamental to realize future telecommunication networks with the exponential growth of internet traffic. Several waveguides, including photonic crystal waveguides,<sup>2-9</sup> semiconductor platforms, 10-14 gold nanowire waveguides, 15 metal slot waveguides, 16 metalinsulator-metal structures, 17 dielectric-metal-dielectric design, 18 dielectric-loaded waveguides, <sup>19</sup> graphene–containing compact microdisks, <sup>20</sup> and optical amplifiers, <sup>21</sup> have been used to create AO logic gates in recent years. The majority of these published designs only used photonic crystals to realize one or, at most, two logic gates, <sup>2-13</sup> in contrast to the suggested waveguide, which simultaneously realized seven logic operations. Furthermore, some of these reported projects have utilized more expensive noble metals, such as gold and silver, 15-19 as compared to the materials (i.e., silicon and silica) used in our design. Therefore, implementing multifunctional logic gates with high contrast ratios (CRs) between the output logic states "1" and "0" based on basic and inexpensive waveguides remains a significant challenge. Additionally, the suggested design can address the expanding need for faster speeds by

0091-3286/2023/\$28.00 © 2023 SPIE

<sup>\*</sup>Address all correspondence to Amer Kotb, amer@ciomp.ac.cn, asm05@fayoum.edu.eg

transmitting data at a high speed of up to 103 Gb/s with higher CRs than other reported designs. 6,10,16-18 From here, we deduce that specialists in the field are still working and will strive to find simpler and less cost designs that meet future needs. Following these significant efforts, we have designed compact SOI waveguides to perform seven basic Boolean logic functions, including XOR, AND, OR, NOT, NOR, NAND, and XNOR operated at a telecommunications wavelength of 1.33  $\mu$ m. It is commonly known that Si has a low loss (<2 dB/cm) for wavelengths up to  $8 \mu m$ ; however, at longer wavelengths, there are multiple multiphonon absorption peaks.  $SiO_2$  optical loss, on the other hand, rapidly increases beyond 3.6  $\mu$ m, making SOI waveguides unsuitable alternatives for longer wavelengths. 22 The proposed device consists of two microring resonators and three strip waveguides, all made of Si patterned on SiO<sub>2</sub>. The operation principle for the realization of the proposed logic operations depends on the constructive and destructive interferences between the incident beams. These logic gates could be implemented by running Lumerical finite-difference-time-domain (FDTD) solutions with the convolutional optimally matched layer as an absorbing boundary condition.<sup>23</sup> The CR is employed to evaluate the operations' performance. This scheme can help with the design and implementation of numerous combinational circuits and subsequent applications, which are required for the creation and realization of lightwave systems and networks that fully exploit the advantages of AO solutions for efficiently satisfying customers' demanding needs.

# 2 SOI Waveguide

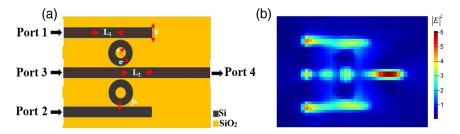

The structure consists of two identical microring resonators and three strips made of Si as core (refractive index  $\sim$ 3.45) patterned on SiO<sub>2</sub> insulator substrate as cladding (refractive index  $\sim$ 1.46). This results in substantially stronger light confinement inside SOI waveguides, which is advantageous for linear and nonlinear light applications as well as optical device size management. The proposed device has three input ports (i.e., ports 1 to 3) and one output port (i.e., port 4). The input ports are exposed to the transverse electric mode polarized wave operating at 1.33  $\mu$ m. The schematic diagram and electric field distributions of the suggested waveguide are illustrated in Fig. 1.

When a beam passes through the two side strips, part of the beam will be coupled into the middle strip through the optical microring resonators. The FDTD intensity monitors are used for recording the light intensities at the input and output ports. The spectral transmission (T) is defined as  $T = I_{\text{out}}/I_{\text{in}} = |E_{\text{out}}|^2/|E_{\text{in}}|^2$ , where  $I_{\text{out}}$  is the intensity at the output port (i.e.,  $P_{\text{out}}$ ), and  $I_{\text{in}} = I_1 + I_2 + I_3$  is the sum of the intensities at the three input ports. The threshold transmission  $(T_{th})$  of 0.2 is first set to decide the desired logic function. The output port (i.e., port 4), produces a logical output of "1" when  $T > T_{th}$ , but in all other circumstances it produces "0." The input beams have the same intensity and wavelength. The incident beams must satisfy the phase-matching requirements for T to be maximized. Researchers are currently concentrating on on-chip optical phase compensation and reconfiguration employing unique techniques that can be separated into dynamic and static phase control schemes. 24,25 A thermooptic phase shifter is employed to regulate the phase between two distinct waveguides on the chip. Over one of the waveguides where a current can flow, a tiny nickel-chromium electrode is directly deposited. The refractive index changes slightly as a result of the local Ohmic heating, thus inducing an optical phase difference between the two different waveguides. This phase can be adjusted across a full range from 0 to  $2\pi$ . The addition of a modified line near the standard waveguide with low laser

Fig. 1 (a) Schematic diagram and (b) electric field distributions of SOI waveguide.

Optical Engineering 048101-2 April 2023 • Vol. 62(4)

Table 1 Simulation parameters.

| Symbol                | Definition                       | Value | Unit    |

|-----------------------|----------------------------------|-------|---------|

| <i>L</i> <sub>1</sub> | Length of side stripes           | 1.0   | μm      |

| $L_2$                 | Length of middle stripe          | 1.5   | $\mu$ m |

| W                     | Width of stripe                  | 0.2   | $\mu$ m |

| d                     | Thickness of stripe              | 0.3   | $\mu$ m |

| а                     | Radius of inner ring             | 0.1   | $\mu$ m |

| b                     | Radius of outer ring             | 0.2   | $\mu$ m |

| $d_r$                 | Distance between stripe and ring | 0.01  | $\mu$ m |

| $\lambda_s$           | Operating wavelength             | 1.33  | $\mu$ m |

| $T_{th}$              | Threshold transmission           | 0.2   |         |

intensity, on the other hand, is employed as a static phase control strategy method. By keeping its single-mode feature, the changed line can change the waveguide's effective refractive index. The modified line can change the effective refractive index of the waveguide by maintaining its single-mode property. Conversely, destructive interference scatters the incident beams and yields a "0" output when the waveguide and incident beams are out of phase. Typically, the CR is defined as  $CR(dB) = 10 \ln[P_{mean}^1/P_{mean}^0]^{14,21}$  takes into account the peak power of all outputs bits (i.e.,  $P_{mean}^1$  and  $P_{mean}^0$ ), while other metrics, such as the extinction ratio, only take into account the peak power of the minimum and maximum outputs "1" and "0," respectively. Thus, the performance of the logic gate design may thus be evaluated more effectively and accurately using the CR. The default parameters indicated in Table 1 were used for all simulations during preparation and execution using FDTD.

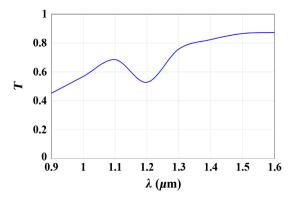

Figure 2 illustrates the spectral transmission (T) utilizing the suggested waveguide as a function of operating wavelength ( $\lambda$ ). The incident beams have been injected at the three input ports with the same 180 deg phase when this figure was obtained. This figure demonstrates how the proposed waveguide maintains high T throughout a broad range of telecommunications wavelengths, from 1.3 to 1.6  $\mu$ m.

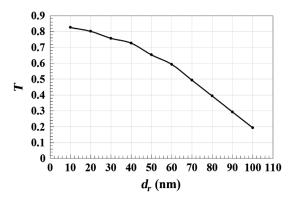

The distance between the strip and ring  $(d_r)$  plays an important role in the proposed design in order to implement the considered logic gates with high CRs. Thus, the effect of  $d_r$  on normalized spectral T at an operating wavelength of 1.33  $\mu$ m is simulated, as shown in Fig. 3. It is clear from this figure that a high T is obtained up to  $d_r = 60$  nm. This result confirms that the proposed design can be fabricated especially with the availability of the 3D capability of the femtosecond laser direct writing technology.  $^{27-36}$

Fig. 2 Spectral transmission (T) versus operating wavelength ( $\lambda$ ) using SOI waveguide.

Optical Engineering 048101-3 April 2023 • Vol. 62(4)

Fig. 3 Normalized spectral transmission (T) versus distance between strip and ring ( $d_r$ ) using SOI waveguide.

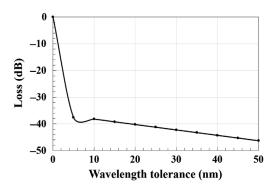

For both production and operating conditions, relaxed tolerances are essential. Production tolerances deal with how geometrical dimensions are handled during processing and how that affects the functionality of the device. While the device's response to changes in wavelength, polarization, temperature, input field distribution, and refractive index is described by operation tolerances. <sup>37,38</sup> Practical wavelength tolerance is generally quite large for laser sources. The actual wavelength of a 1330-nm laser diode, for instance, can be  $1330 \pm 10$  nm due to a wavelength tolerance of  $\pm 10$  nm. <sup>39</sup> The dependence of the loss on the wavelength tolerance using the SOI waveguide is depicted in Fig. 4 based on Eqs. (4)–(7). <sup>40</sup>

Shannon-Hartely developed a theoretical formula for calculating the transmission rate; however, they also took into account the signal-to-noise ratio. Shannon-Hartely expresses the speed of transmission as  $B \log_2[1 + \text{SNR}]$ , where B is the optical bandwidth, which is defined as  $B = (c/\lambda^2)\Delta\lambda$ , where c is the speed of light in vacuum,  $\lambda = 1.33~\mu\text{m}$  is the optical carrier wavelength, and  $\Delta\lambda$  is the signal's spectral width. SNR =  $P_{\text{out}}/\text{kTB}$ , where  $P_{\text{out}}$  is the total output power; k is Boltzmann's constant; and T is the absolute temperature. This means that in our case at room temperature (i.e., T = 295~k), where  $P_{\text{out}} = 0.16~\mu\text{W}$  and B = 8.48~GHz, the speed is 103~Gb/s.

The components Si and SiO<sub>2</sub> used in the proposed waveguide are widely distributed in the earth's crust and have a major impact on the mantle's composition. The primary findings of this simulation can therefore be used as a foundation for experimental verification of the proposed waveguide, given that the required technology is accessible. Numerous optical logic functions, on the other hand, are implementable experimentally based on various waveguides. <sup>10,12,15,42,43</sup> Additional electrical and optical components, such as laser sources, couplers, fibers, phase shifters, amplifiers, filters, etc., should unquestionably be needed for the whole experimental setup for creating logical operations. <sup>44–46</sup>

Fig. 4 Loss versus wavelength tolerance using SOI waveguide.

Optical Engineering 048101-4 April 2023 • Vol. 62(4)

Fig. 5 XOR field intensity distributions using SOI waveguide at 1.33  $\mu$ m.

## 3 Gates' Implementation

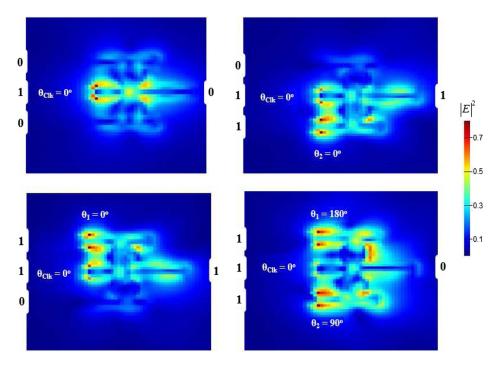

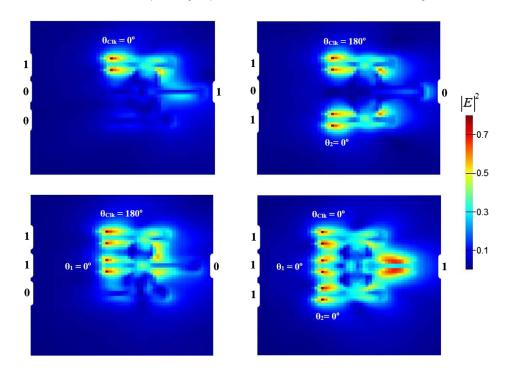

## **3.1** XOR

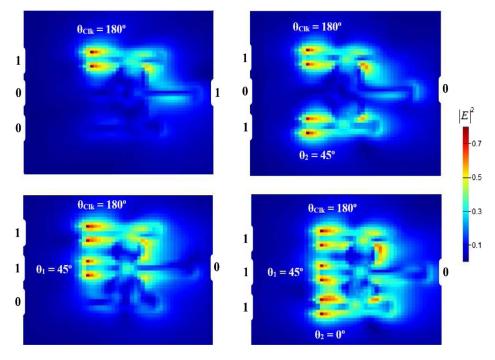

The XOR gate gives a "1" output if only one of its inputs is "1". To perform the XOR gate, two input beams are injected into the scheme from ports 1 and 2, respectively. The clock light (Clk) is launched into the middle port (i.e., port 3) while port 4 acts as the output port (see Fig. 1). The Clk (all "1's") should be utilized to produce an input beam reference phase difference that results in either constructive or destructive interference. When two input beams are "0" and "1," or vice versa (i.e., 01 or 10) and Clk all adjusted with the same phase of 0 deg, port 4 generates a higher T than  $T_{\rm th}$  due to the constructive interference, resulting in "1" output. When both input beams are "1" having  $\Delta\theta = 90$  deg and Clk having  $\theta_{\rm Clk} = 0$  deg, the output of port 4 produces "0" due to the destructive interference between the input beams. The field intensity distributions for the logic XOR gate at 1.33  $\mu$ m are illustrated in Fig. 5.

Table 2 summarizes the simulation results for the XOR gate. High CR = 25.67 dB is obtained due to the relatively slight difference between the mean peak powers of logical "1" and logical "0".

# **3.2** AND

"1" output results only if all the inputs to the AND gate are "1". Two beams are inserted from ports 1 and 2, while the Clk (all "1's") is inserted from port 3 to perform the AND operation

Port 2 Port 3 (Clk) Port 4 (output) Τ Port 1 CR (dB) 0 0 0 0.037 25.67 0 1 1 1 0.514 0 1 1 0.514 0.042

**Table 2** XOR simulation results ( $T_{th} = 0.2$ ).

Optical Engineering 048101-5 April 2023 • Vol. 62(4)

**Fig. 6** AND field intensity distributions using SOI waveguide at 1.33  $\mu$ m.

| Port 1 | Port 2 | Port 3 (Clk) | Port 4 (output) | Т     | CR (dB) |

|--------|--------|--------------|-----------------|-------|---------|

| 0      | 0      | 1            | 0               | 0.037 | 32.73   |

| 0      | 1      | 1            | 0               | 0.029 |         |

| 1      | 0      | 1            | 0               | 0.029 |         |

| 1      | 1      | 1            | 1               | 0.826 |         |

**Table 3** AND simulation results ( $T_{th} = 0.2$ ).

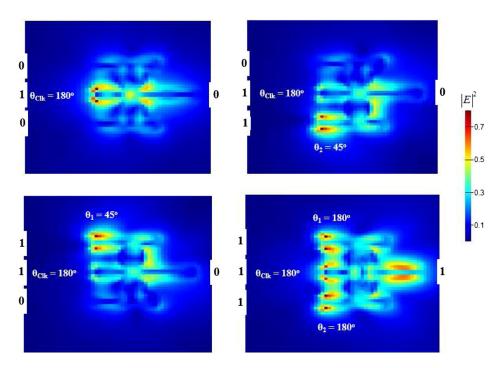

(see Fig. 1). When the input beams are "1" and "0" or vice versa, the destructive interference results in "0" at port 4 due to the phase difference between the input beams. When both input beams are "1," port 4 generates "1" output due to the constructive interference, occurring as a result of the same phases of the input beams and Clk, i.e.,  $\theta_1 = \theta_2 = \theta_{\text{Clk}} = 180$  deg. This is functionally equivalent to the AND logic operation. Figure 6 shows the AND field intensity distributions at 1.33  $\mu$ m.

Table 3 shows that the value of the CR = 32.73 dB is very high due to the extreme difference between the mean peak powers of "1" and "0".

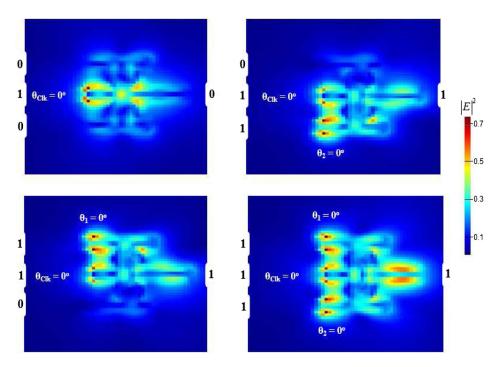

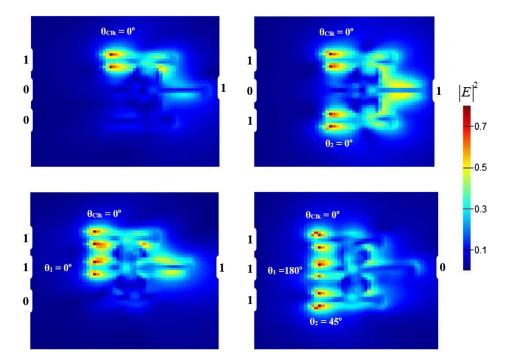

#### 3.3 OR

The logic OR gate results in "1" output only when one or more of its inputs are "1". For the OR gate, two input beams are supplied into the waveguide from ports 1 and 2, while the Clk is injected into the middle port (i.e., port 3). The OR gate can be realized when the input beams and Clk are propagating with the same phase, i.e.,  $\theta_1 = \theta_2 = \theta_{\text{Clk}} = 0$  deg. Therefore, the normalized T is enhanced by the constructive interference between the input beams. The field intensity distributions for the logic OR gate are depicted in Fig. 7 at 1.33  $\mu$ m.

Table 4 shows the simulation findings in terms of normalized T and CR for the OR gate at 1.33  $\mu$ m.

Optical Engineering 048101-6 April 2023 • Vol. 62(4)

Fig. 7 OR field intensity distributions using SOI waveguide at 1.33  $\mu$ m.

| Port 1 | Port 2 | Port 3 (Clk) | Port 4 (output) | Т     | CR (dB) |

|--------|--------|--------------|-----------------|-------|---------|

| 0      | 0      | 1            | 0               | 0.037 | 28.43   |

| 0      | 1      | 1            | 1               | 0.514 |         |

| 1      | 0      | 1            | 1               | 0.514 |         |

| 1      | 1      | 1            | 1               | 0.826 |         |

**Table 4** OR simulation results ( $T_{\rm th}=0.2$ ).

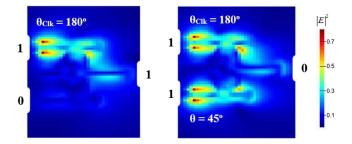

## **3.4** *NOT*

The NOT or invert gate provides a "1" output if the input is "0" and vice versa. For the NOT gate, a Clk (all 1's) with  $\theta_{\rm Clk}=180$  deg and an input beam with  $\theta=45$  deg are injected into the proposed structure from ports 1 and 2, respectively. When port 2 is "1", the input beams experience differing phases to destructively interfere, thereby resulting in a logical "0" at the output of port 4. When port 2 is "OFF", the Clk does not experience any phase difference, resulting in logical "1" at port 4. This procedure is analogous to the logic NOT gate. The NOT field intensity distributions at 1.33  $\mu$ m are shown in Fig. 8.

Fig. 8 NOT field intensity distributions using SOI waveguide at 1.33  $\mu m$ .

Optical Engineering 048101-7 April 2023 • Vol. 62(4)

**Table 5** NOT simulation results ( $T_{th} = 0.2$ ).

| Port 1 (Clk) | Port 2 | Port 4 (output) | Т     | CR (dB) |

|--------------|--------|-----------------|-------|---------|

| 1            | 0      | 1               | 0.310 | 11.78   |

| 1            | 1      | 0               | 0.037 |         |

The simulation results for logic NOT gate are summarized in Table 5. These results show that the NOT logic gates can be implemented at 1.33  $\mu$ m with better CR = 11.78 dB using the proposed scheme.

#### **3.5** NOR

An output "1" results if both the inputs to the NOR (NOT-OR) gate are "0". To perform NOR, the Clk is injected into port 1, while the two input beams are injected into ports 2 and 3 in Fig. 1. Thus, when a combination of input beams is (01, 10, or 11), the logic output is "0" due to the phase difference that leads to destructive interference. When beams with the combination (00) are launched at  $\Delta\theta=0$  deg, the Clk beam at  $\theta_{\rm Clk}=180$  deg breaks the phase balance, resulting in a logical "1" at port 4 due to constructive interference. The Boolean NOR logic gate is thus realized as depicted in Fig. 9.

Table 6 summarizes the simulation results for the NOR gate with CR = 23.70 dB.

#### **3.6** *NAND*

NAND gate (NOT-AND) produces a "0" output only if all its inputs are "1". The NAND gate can be performed by injecting the Clk into port 1 while the two other input beams are launched into ports 2 and 3, respectively. When (00) is launched, the output is "1" due to the Clk injected into with  $\theta_{\text{Clk}}=0$  deg. In this case, the spectral T value is slightly above the  $T_{\text{th}}$ . When (01, 10) is launched with the same phase (i.e.,  $\Delta\theta=0$  deg), constructive interference occurs, resulting in a "1" output. Destructive interference happens at port 4 when (00) is launched at different phases, i.e.,  $\theta_1=180$  deg,  $\theta_2=45$  deg, and  $\theta_{\text{Clk}}=0$  deg, as shown in Fig. 10.

**Fig. 9** NOR field intensity distributions using SOI waveguide at 1.33  $\mu$ m.

Optical Engineering 048101-8 April 2023 • Vol. 62(4)

**Table 6** NOR simulation results ( $T_{th} = 0.2$ ).

| Port 1 (Clk) | Port 2 | Port 3 | Port 4 (output) | Т     | CR (dB) |

|--------------|--------|--------|-----------------|-------|---------|

| 1            | 0      | 0      | 1               | 0.310 | 23.70   |

| 1            | 0      | 1      | 0               | 0.030 |         |

| 1            | 1      | 0      | 0               | 0.027 |         |

| 1            | 1      | 1      | 0               | 0.034 |         |

Fig. 10 NAND field intensity distributions using SOI waveguide at 1.33  $\mu m$ .

Table 7 NAND simulation results ( $T_{\rm th}=0.2$ ).

| Port 1 (Clk) | Port 2 | Port 3 | Port 4 (output) | Т     | CR (dB) |

|--------------|--------|--------|-----------------|-------|---------|

| 1            | 0      | 0      | 1               | 0.290 | 30.50   |

| 1            | 0      | 1      | 1               | 0.735 |         |

| 1            | 1      | 0      | 1               | 0.684 |         |

| 1            | 1      | 1      | 0               | 0.027 |         |

The simulation results for the NAND gate are listed in Table 7. The mean peak power of "1" output is higher than that of "0" producing a high CR = 30.50 dB.

# **3.7** XNOR

An output "1" results if both of the inputs to the XNOR gate are the same (i.e., 00 or 11). As in the NOR and NAND gates, the Clk is going into port 1, while the two beams are into ports 2 and 3, respectively. Both constructive and destructive interferences between the Clk and the input beams are used to perform the XNOR gate. The output port is "1" when input beams'

Optical Engineering 048101-9 April 2023 • Vol. 62(4)

**Fig. 11** XNOR field intensity distributions using SOI waveguide at 1.33  $\mu$ m.

| Port 1 (Clk) | Port 2 | Port 3 | Port 4 (output) | Т     | CR (dB) |

|--------------|--------|--------|-----------------|-------|---------|

| 1            | 0      | 0      | 1               | 0.310 | 30.85   |

| 1            | 0      | 1      | 0               | 0.027 |         |

| 1            | 1      | 0      | 0               | 0.025 |         |

| 1            | 1      | 1      | 1               | 0.827 |         |

**Table 8** XNOR simulation results ( $T_{th} = 0.2$ ).

combination (00) or (11) is inserted with the same phase, producing constructive interference. By contrast, the output port is "0" when the beams' combination (01) or (10) are launched with different phases, creating destructive interference (Fig. 11).

Because of the wide disparity in the mean peak powers of the "1" and "0" bits, the XNOR gate has a high CR = 30.85 dB. The XNOR simulation results are summarized in Table 8.

## 4 Comparison

Table 9 summarizes various reported structures operated at different wavelengths for implementing AO logic operations. According to this table, the suggested waveguide can perform logic operations with higher CRs than the other listed schemes.

## 5 Applications

Possible drawbacks of the analyzed subsystem can be identified concerning issues such as cascadability and scalability. The proposed waveguide is more scalable, as it is simple to use to implement more combinational logic circuits, such as adders and latches. Besides, the operating wavelengths can be turned on or off on demand, which allow for the easy provisioning of services and quick scaling for a growing network. The proposed waveguide is also small and light.

Optical Engineering 048101-10 April 2023 • Vol. 62(4)

**Table 9** Comparison of implemented AO logic gates using various structures at different wavelengths.

| Operations                            | Structure                            | Wavelength (nm) | CR (dB)        | References |

|---------------------------------------|--------------------------------------|-----------------|----------------|------------|

| AND, XOR, OR, NOT,<br>NAND, NOR XNOR  | Photonic crystal waveguides          | 1550            | 5.42 to 9.59   | 6          |

| AND, XOR, OR                          | T-shaped photonic crystal waveguides | 1550            | 8.29 to 33.05  | 7–9        |

| AND, NOR, XNOR                        | Si photonics platform                | 1550            | >10 dB         | 10         |

| NOT, XOR, AND, OR,<br>NOR, NAND, XNOR | Metal slot waveguide                 | 632.8           | 6 to 16        | 16         |

| NOT, XOR, AND, OR,<br>NOR, NAND, XNOR | Metal-insulator-metal structures     | 632.8           | 15             | 17         |

| NOT, XOR, AND, OR,<br>NOR, NAND, XNOR | Dielectric-metal-dielectric design   | 900 and 1330    | 5.37 to 22     | 18         |

| NOT, XOR, AND, OR,<br>NOR, NAND, XNOR | SOI waveguides                       | 1330            | 11.78 to 32.73 | This work  |

It can typically be placed in optical computers for growth needs up to 15 to 20 years in the future. Furthermore, additional optical components can be installed later to make way for network expansion. However, the optical losses limit the scalability.<sup>47</sup> Thus, the losses must be minimized at the coupling interfaces between the strips and microrings by optimizing the waveguide operational parameters as in our case. On the other hand, the fan-out capability should be attainable in a straightforward manner so as to facilitate the process of building more complex all-optical circuits of enhanced functionality. However, in our case, the operation of the reconfigurable gates is sensitive to the phase of the input beams, whose wavelengths must be carefully assigned. The gates should be able to accommodate more than two input data beams towards implementing multibit logic processing and constructing large switch fabrics. However, increasing the number of data inputs could complicate the process of managing the broadened spectra of these beams. These spectra should be suppressed so as not to spectrally overlap with that of the clock and deteriorate the performance of the gates. Still, these drawbacks are compensated for by the potential of the scheme to realize a suite of different logic functions without change in its fundamental design or architecture. In particular, these logic functions, including XOR, AND, OR, and INVERT, are fundamental in the implementation of various AO systems, such as packet switches, binary adders, binary counters, decision circuits, optical processors, data encoders, parity generation and checking, encryption/decryption, bit pattern recognition circuits, and complex combinational logic circuits. Depending on the outcomes of this simulation, these computational logic circuits can be easily implemented. For example, the SUM and CARRY are two logic functions necessary to realize a binary half-adder. The logical outcome of the SUM function is "1" when only both inputs are "1" and "0," which is equivalent to the logical XOR operation. The logical outcome of the CARRY function is "1" when only both inputs are "1," which is equivalent to the logic AND gate. 48 These two functions are then routed through a similar operation with suitable delay to carry out a full-adder function. 49 The AO latches are also one of the most fundamental sequential logic circuits. 2-input NAND logic gates connected is the simplest approach to build a set-reset latch while two logic functions NAND and NOT are used to build the D flip-flop.<sup>50</sup> The other AO JK and T flip-flops are also can be performed.<sup>51</sup> The parity generator can be also constructed using optical XOR gates. 49 The AO pseudorandom bit stream generators can be made with an optical delay line and XOR gates.<sup>49</sup> Additionally, OA encoder, half-subtractor, and comparator logic circuits can also be performed based on AND, NOR, and XNOR logic gates. 52,53 These logic functions have relied on the compactness, low power consumption, and integrability of the proposed SOI waveguide.

#### 6 Conclusions

We implemented a whole set of fundamental optical logic operations, including XOR, AND, OR, NOT, NOR, NAND, and XNOR, operated at a telecommunications wavelength of 1.33  $\mu$ m using compact silicon-on-silica waveguides. Lumerical FDTD solutions were employed to simulate these operations. Two ring resonators and three identical slots make up the suggested microwaveguide. The proper operation of these logic gates is based on the constructive and destructive interferences that are caused by the phase difference of the input beams. With a speed of 103 Gb/s, the proposed waveguide achieves higher CR values than those previously reported.

### **Acknowledgments**

Amer Kotb thanks the Chinese Academy of Sciences President's International Fellowship Initiative (Grant No. 2022VMB0013) for supporting this work. No potential conflict of interest was reported by the authors.

#### References

- X. C. Tong, "Silicon-on-insulator waveguides," in *Advanced Materials for Integrated Optical Waveguides*, Springer Series in Advanced Microelectronics, Vol. 46, pp. 253–287, Springer, Cham (2014).

- 2. C. Husko et al., "Ultracompact all-optical XOR logic gate in a slow-light silicon photonic crystal waveguide," *Opt. Express* **19**, 20681–20690 (2011).

- 3. P. Andalib and N. Granpayeh, "All-optical ultracompact photonic crystal AND gate based on nonlinear ring resonators," *J. Opt. Soc. Am. B* **26**, 10–16 (2009).

- 4. V. Jandieri, R. Khomeriki, and D. Erni, "Realization of true all-optical AND logic gate based on the nonlinear coupled air-hole type photonic crystal waveguide," *Opt. Express* **26**, 19845–19853 (2018).

- Y. Ishizaka, Y. Kawaguchi, K. Saitoh, and M. Koshiba, "Design of ultracompact all-optical XOR and AND logic gates with low power consumption," *Opt. Commun.* 284, 3528–3533 (2011).

- 6. P. Rani, Y. Kalra, and R. K. Sinha, "Design of all optical logic gates in photonic crystal waveguides," *Optik* **126**, 950–955 (2015).

- 7. N. H. Priya et al., "Design and analysis of an optical three-input AND gate using a photonic crystal fiber," *Appl. Opt.* **61**, 77–83 (2022).

- 8. N. H. Priya et al., "Design and analysis of a photonic crystal-based all-optical 3-input OR gate for high-speed optical processing," *Opt. Quantum Electron.* **53**, 720 (2021).

- 9. D. G. S. Rao et al., "Design of all-optical AND, OR, and XOR logic gates using photonic crystals for switching applications," *Photonics Netw. Commun.* **41**, 109–118 (2021).

- S. Kita et al., "Ultrashort low-loss Ψ gates for linear optical logic on Si photonics platform," Commun. Phys. 3, 33 (2020).

- 11. S. Zeng, Y. Zhang, and E. Pun, "Ultrasmall optical logic gates based on silicon periodic dielectric waveguides," *Photon. Nanostr. Fundam. Appl.* **8**, 32 (2010).

- 12. L. Cui and L. Yu, "Multifunctional logic gates based on silicon hybrid plasmonic waveguides," *Mod. Phys. Lett. B* **32**, 1850008 (2018).

- 13. T. A. Ibrahim et al., "All-optical AND/NAND logic gates using semiconductor microresonators," *IEEE Photon. Technol. Lett.* **15**, 1422–1424 (2003).

- 14. A. Kotb and K. E. Zoiros, "K-shaped silicon waveguides for logic operations at 1.55  $\mu$ m," *Electronics* **11**, 3748 (2022).

- 15. L. Gao et al., "Lithographically fabricated gold nanowire waveguides for plasmonic routers and logic gates," *Nanoscale* **10**, 14771 (2018).

- D. Pan, H. Wei, and H. Xu, "Optical interferometric logic gates based on metal slot waveguide network realizing whole fundamental logic operations," *Opt. Express* 21, 9556 (2013).

- 17. Y. Bian and Q. Gong, "Compact all-optical interferometric logic gates based on one-dimensional metal-insulator-metal structures," *Opt. Commun.* **313**, 27–35 (2014).

- 18. H. K. Al-Musawi et al., "Plasmonic logic gates based on dielectric-metal-dielectric design with two optical communication bands," *Optik* **223**, 165416 (2020).

- 19. C. Yao et al., "All-optical logic gates using dielectric-loaded waveguides with quasi-rhombus metasurfaces," *Opt. Lett.* **45**, 3769–3772 (2020).

- 20. P. Keshtkar, M. Miri, and N. Yasrebi, "Low power, high speed, all-optical logic gates based on optical bistability in graphene-containing compact microdisk resonators," *Appl. Opt.* **60**, 7234–7242 (2021).

- A. Kotb and C. Guo, "100 Gb/s all-optical multifunctional AND, XOR, NOR, OR, XNOR, and NAND logic gates in a single compact scheme based on semiconductor optical amplifiers," *Opt. Laser Technol.* 137, 106828 (2021).

- 22. G. Z. Mashanovich et al., "Low loss silicon waveguides for the mid-infrared," *Opt. Express* **19**, 7112–7119 (2011).

- 23. I. Laakso, S. Ilvonen, and T. Uusitupa, "Performance of convolutional PML absorbing boundary conditions in finite-difference time-domain SAR calculations," *Phys. Med. Biol.* **52**, 7183–7192 (2007).

- 24. B. J. Smith et al., "Phase-controlled integrated photonic quantum circuits," *Opt. Express* 17, 13516–13525 (2009).

- 25. Y. Wang et al., "Phase customization in photonic integrated circuits with trimmed waveguides," *Opt. Lett.* **47**, 5889–5892 (2022).

- 26. K. E. Zoiros et al., "Theoretical analysis and performance investigation of ultrafast all-optical Boolean XOR gate with semiconductor optical amplifier-assisted Sagnac interferometer," *Opt. Commun.* **258**, 114–134 (2006).

- 27. M. Li et al., "On-chip path encoded photonic quantum Toffoli gate," *Photonics Res.* **10**, 1533–1542 (2022).

- 28. F. Klauck, M. Heinrich, and A. Szameit, "Photonic two-particle quantum walks in Su-Schrieffer-Heeger lattices," *Photonics Res.* **9**, A1–A7 (2021).

- 29. Q. Zhang et al., "Reconfigurable directional coupler in lithium niobate crystal fabricated by three-dimensional femtosecond laser focal field engineering," *Photonics Res.* **7**, 503–507 (2019).

- 30. C. Anton et al., "Interfacing scalable photonic platforms: solid-state based multi-photon interference in a reconfigurable glass chip," *Optica* **6**, 1471–1477 (2019).

- 31. S. Atzeni et al., "Integrated sources of entangled photons at the telecom wavelength in femtosecond-laser-written circuits," *Optica* 5, 311–314 (2018).

- 32. D. Wei et al., "Experimental demonstration of a three-dimensional lithium niobate nonlinear photonic crystal," *Nat. Photonics* **12**, 596–600 (2018).

- 33. J. Ni et al., "Three-dimensional chiral microstructures fabricated by structured optical vortices in isotropic material," *Light Sci. Appl.* **6**, e17011 (2017).

- 34. M. A. Ciampini et al., "Path-polarization hyperentangled and cluster states of photons on a chip," *Light Sci. Appl.* **5**, e16064 (2016).

- 35. R. Kammel et al., "Enhancing precision in fs-laser material processing by simultaneous spatial and temporal focusing," *Light Sci. Appl.* **3**, e169 (2014).

- 36. G. D. Marshall et al., "Laser written waveguide photonic quantum circuits," *Opt. Express* 17, 12546–12554 (2009).

- V. M. N. Passaro and M. L. Notte, "Optimizing SOI slot waveguide fabrication tolerances and strip-slot coupling for very efficient optical sensing," *Sensors* 12, 2436–2455 (2012).

- 38. A. Prinzen, M. Waldow, and H. Kurz, "Fabrication tolerances of SOI based directional couplers and ring resonators," *Opt. Express* **21**, 17212–17220 (2013).

- 39. https://www.laserdiodesource.com/shop/1330nm-5mw-DFB-PD-APC-fiber-coupled-WVSL

- A. M. Al-Hetara and Z. A. Shamsan, "Optical wavelength and dimensions tolerance criterion for multimode interference couplers," WSEAS Trans. Commun. 13, 567–571 (2014).

- 41. J. Crisp and B. Elliott, Introduction to Fiber Optics, 3rd ed., Elsevier, Amsterdam (2005).

- 42. V. Donzella et al., "Design and fabrication of SOI micro-ring resonators based on sub-wavelength grating waveguides," *Opt. Express* **23**, 4791–4803 (2015).

- 43. Y. Fu et al., "All-optical logic gates based on nanoscale plasmonic slot waveguides," *Nano. Lett.* **12**, 5784–5790 (2012).

- 44. X. Chen et al., "Study on 100-Gb/s reconfigurable all-optical logic gates using a single semiconductor optical amplifier," *Opt. Express* **24**, 30245–30253 (2016).

- 45. H. Dong et al., "80 Gb/s All-optical logic AND operation using Mach-Zehnder interferometer with differential scheme," *Opt. Commun.* **265**, 79–83 (2006).

- 46. Q. Wang et al., "Study of all-optical XOR using Mach–Zehnder interferometer and differential scheme," *IEEE J. Quantum Electron.* **40**, 703–710 (2004).

- 47. I. T. Monroy and E. Tangdiongga, *Crosstalk in WDM Communication Networks*, Springer, Germany (2007).

- 48. A. Kotb et al., "All-optical half adder using carrier reservoir semiconductor optical amplifiers at 120 Gb/s," *Pramana-J. Phys.* **96**, 154 (2022).

- 49. N. K. Dutta and Q Wang, *Semiconductor Optical Amplifiers*, 2nd ed., World Scientific, Singapore (2013).

- 50. A. Kotb, K. E. Zoiros, and W. Li, "All-optical latches using carrier reservoir semiconductor optical amplifiers," *Opt. Laser Technol.* **157**, 108737 (2023).

- 51. G. K. Bharti and J. K. Rakshit, "Design of all-optical JK, SR and T flip-flops using microring resonator-based optical switch," *Photonics Netw. Commun.* **35**, 381–391 (2018).

- 52. S. H. Abdulnabi and M. N. Abbas, "Design an all-optical combinational logic circuits based on nano-ring insulator-metal-insulator plasmonic waveguides," *Photonics* **6**, 30 (2019).

- 53. Y. Wang et al., "Simultaneous demonstration on all-optical digital encoder and comparator at 40 Gb/s with semiconductor optical amplifiers," *Opt. Express* **15**, 15080–15085 (2007).

Biographies of the authors are not available.