## Opto-Electronic Engineering

文章编号: 1003-501X(2011)09-0019-06

# 高速多光谱 TDICCD 图像数据传输系统

朱宏殷1,2,郭永飞1,石俊霞1,2,司国良1

(1. 中国科学院长春光学精密机械与物理研究所,长春 130033;

2. 中国科学院研究生院, 北京 100049)

摘要: 为了解决高速多通道 CCD 应用时数据传输路数多、数据率高的问题,研制了高速多光谱 TDICCD 的图像数据传输系统,并在实际工程应用中取得良好效果。阐述了系统总体设计思想和 FPGA 实现方案,并对 FPGA 功能划分、时分复用存储及 LVDS 接口等设计要点进行详细分析,最终系统实现了 5 片 TDICCD 共 60 通道并行图像数据转 7 路串行图像数据输出。实验结果表明,单路数据率最高达到 1.38 Gbit/s,系统总有效数据率达到 8.66 Gbit/s,且系统稳定可靠,方便移植。

关键词: 高速; 多光谱 TDICCD; FPGA; 数据传输

中图分类号: V443.5

文献标志码: A

doi: 10.3969/j.issn.1003-501X.2011.09.004

# **High-speed Multi-spectral TDICCD Image Data Transmission System**

ZHU Hong-yin<sup>1,2</sup>, GUO Yong-fei<sup>1</sup>, SHI Jun-xia<sup>1,2</sup>, SI Guo-liang<sup>1</sup>

(1. Changchun Institute of Optics, Fine Mechanics and Physics, Chinese Academy of Sciences, Changchun 130033, China; 2. Graduate University of Chinese Academy of Sciences, Beijing 100049, China)

**Abstract**: For multi-channel high-speed Charge Couple Device (CCD) image data transmission, a new high-speed multi-spectral Time Delay Integrated CCD (TDICCD) image data transmission system was designed and applied successfully. Overall system design principle and realization in FPGA were introduced. Especially, the key technology such as Field Programmable Gate Array (FPGA) function division, time-division multiplexing storage and Low Voltage Differential Signaling (LVDS) interface were described in detail. Finally, 60 channels' parallel image data of 5 TDICCD were converted into 7 channels serial image data. Experiments show that the system's single channel output data rate is up to 1.38 Gbit/s, and total effective data output rate is up to 8.66 Gbit/s. The system works stably with high effective and transplantable property.

Key words: high-speed; multi-spectral TDICCD; FPGA; data transmission

# 0 引 言

TDICCD 可以利用多级感光区通过光延迟积分的方式对同一运动目标多次曝光,多次曝光收集的电荷之和作为该目标在 CCD 内所成的像,所以,TDICCD 相机与传统 CCD 相机相比,成像灵敏度和信噪比都得到有效提高,从而相机重量、体积、功耗和成本都有效降低<sup>[1-2]</sup>。随着对地面获取特定资源数据能力的需求不断增加,如进行绿色资源评价、矿物资源探测等,多光谱相机越来越受到青睐。因此,高分辨率遥感相机把 TDICCD 作为首选探测器,探测器上既包括可见光谱段又包括多光谱谱段。

由于遥感相机对分辨率和视场宽度要求的不断增加<sup>[3]</sup>,所采用的 CCD 读出像元速率、读出像元通道数和 CCD 拼接片数都在不断提高,从而单位时间内需要输出的 CCD 数字图像数据量急剧增大,这给遥感相

收稿日期: 2011-04-27; 收到修改稿日期: 2011-06-20

基金项目: 中科院国防创新基金资助项目

作者简介: 朱宏殷(1984-),女(汉族),黑龙江大庆人。博士研究生,主要研究光电成像技术及 FPGA 应用技术。 E-mail: zhuhongyin\_190310@163.com。 机图像数据传输系统的设计提出了很大的挑战。国内外学者在这方面做了很多研究,文献[4]报导的 640×512 像素 14 bit 24 通道凝视焦平面成像系统均采用多通道采集技术,并获得较好的性能。但其设计系统体积庞大,进一步提高指标的话会使系统复杂度加剧,不满足遥感相机轻小型化的需求。文献[5]介绍了 16 MHz 像元读出速率的 10 bit 8 通道单片 TDICCD 信号并行处理系统,但其没有对更多像元通道数和更高的像元读出速率进行探讨。

本文在相关研究技术的基础上,结合工程需求,设计了高速多光谱 TDICCD 图像数据传输系统,该系统采用两级数据整合方式,可同时传输 5 片高速多光谱 TDICCD 的图像数据,总有效数据实时传输率达 8.66 Gbit/s,且可靠稳定,对其它相关工程具有实际参考意义。

### 1 TDICCD 简介

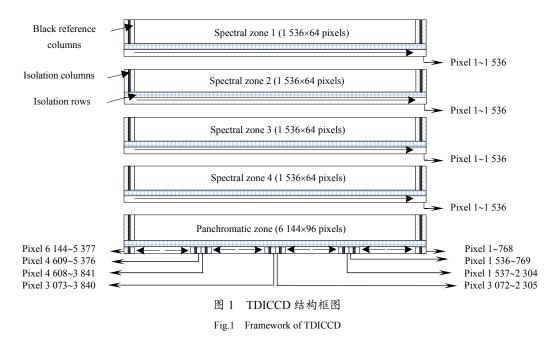

TDICCD 是一种面阵结构、线阵输出的  $CCD^{[2]}$ ,本文所研究的 TDICCD 的结构框图如图 1 所示,共有五个成像区,每个成像区内的有效像元阵列呈  $M \times N$  结构排列,M 为水平方向的像元数,即一行图像的有效像元个数,N 为垂直方向的像元数,即积分级数。对于 4 个多光谱成像区 M 为 1 536,分别从四个抽头输出,N 为 64;全色成像区 M 为 6 144,从 8 个抽头输出,每个抽头输出像元顺序如图 1 所示,N 为 96。像元读出速率最高可达到 24 MHz。水平和垂直方向电荷的顺序读出是通过对水平移位寄存器和垂直移位寄存器的驱动来实现的,积分级数分六档可调。每个成像区除有效像元外,还设有暗参考像元、隔离列像元和隔离行像元。暗参考像元对光屏蔽,起参考作用。在暗参考像元的两侧分别加入几列隔离列像元,与成像像元进行隔离。隔离行像元位于第一个开始积分的行之前。TDICCD 具体成像原理在文献[6]、[7]中有详细描述,本文不再赘述。

2 系统设计

#### 2.1 总体设计思想

相机焦平面由 5 片 TDICCD 机械拼接而成,每片 TDICCD 同时输出包含一个全色谱段和四个多光谱谱 段共分 12 通道的图像数据,则系统需要对 12 位量化后高达 720 位的并行图像数据进行实时处理并高速传输。如果完全并行处理的话,数据传输可靠性高,但是占用 I/O 资源巨大,给数据处理系统和后续载荷数据处理单元的 I/O 端口都造成巨大压力,并且极大的增加数据传输线缆数量,从而增加相机重量和系统互连复杂度。如果完全串行处理的话,需要非常高的数据传输速率,对数据处理系统的主处理器速率和数据

传输带宽要求都特别高,不易实现,而且高速还可能增加系统误码率。

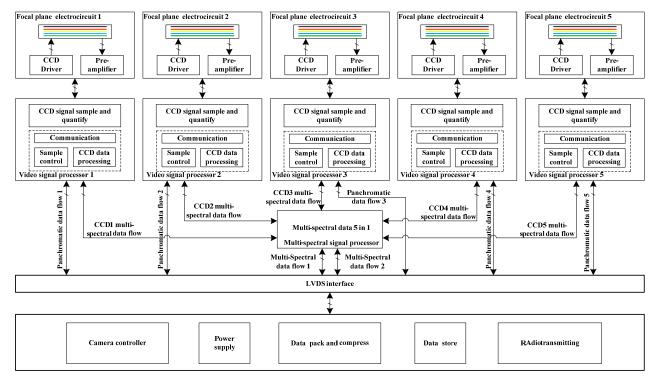

综合考虑系统特点以及并行传输和串行传输各有优缺点,本系统采用并串结合的方式进行传输。该系统的结构框图如图 2 所示,并行是指 5 片 CCD 共 60 通道的图像数据分为 5 个区域并行处理,即每片 CCD 由 1 个焦平面电路单元进行驱动和模拟信号预处理,输出的可见光和多光谱图像数据由 1 个视频信号处理单元进行控制和处理,5 片 CCD 则对应 5 个焦平面电路单元和 5 个视频信号处理单元。串行是指为了充分利用处理器的能力、减少 I/O 端口资源消耗和降低对下级系统的互连复杂度,分别对每片 CCD 的 8 通道可见光图像数据和 4 通道多光谱图像数据在对应的视频信号处理单元进行一级数据整合,再在多光谱信号处理单元对一级整合后的多光谱图像数据进行二级数据整合。

图 2 系统结构框图

Fig.2 Block diagram of system

#### 2.2 FPGA 设计

在图像数据传输过程中,视频信号处理单元和多光谱信号处理单元上的主处理器的选择十分重要,其既要有较高的处理速率、大容量的内嵌 RAM 又要有丰富的 I/O 资源,最终选用 FPGA 作为两个处理单元的主处理器,具体型号为 VirtexII系列的 XC2V3000 芯片,它有 700 多 I/O 管脚,内嵌 1 728 Kbits 的 BRAM (Block Radom Access Memory)以及 12 个 DCM<sup>[8]</sup>。为便于区分视频信号处理单元 FPGA 和多光谱信号处理单元 FPGA,分别将其简称为全色 FPGA 和多光谱 FPGA。

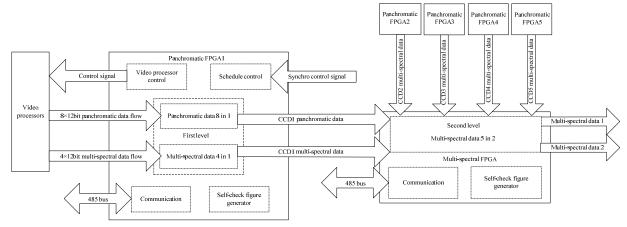

全色 FPGA 主要有六个功能模块,多光谱 FPGA 主要有三个功能模块,其所完成的功能如图 3 所示。全色 FPGA 向集成视频处理器发送控制信号进行 CDS(Correlation Double Sample)、PGA(Programmable Gain Amplifier)和 ADC(Analog to Digital Converter)等控制,经视频处理器采样量化后的 8 通道 12 位全色数据流和 4 通道 12 位多光谱数据流在全色 FPGA 内部完成一级数据整合,生成按像元 1~像元 6 144 排列的 CCDN 全色图像数据流和按谱段 1~谱段 4 排列的 CCDN 多光谱图像数据流;一级整合后 CCD1~ CCD5 的多光谱图像数据再送入多光谱 FPGA 内进行二级数据整合,最终生成两路多光谱图像数据流。全色 FPGA 和多光谱 FPGA 均通过 485 总线与相机控制器进行通讯,接收指令,返回遥测参数。自校图形产生模块是产生一系列具有规律的数据来模拟 CCD 数据,便于对可能出现的故障进行剥离和定位。全色 FPGA 中的时序控制模块接收相机控制器的同步控制信号,再产生内同步信号对 FPGA 内各模块工作时序进行同步控制。在

FPGA 程序设计时采用同步设计方法和流水线设计思想。

图 3 FPGA 内部功能框图

Fig.3 FPGA function block diagram

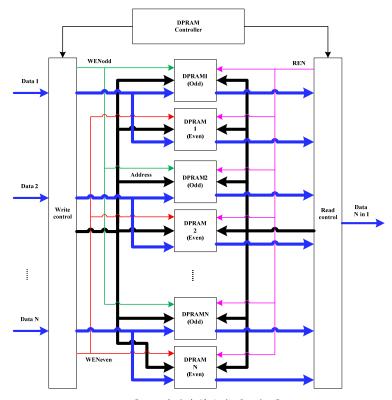

#### 2.3 图像数据乒乓存储

将 FPGA 内嵌 BRAM 设置成 DPRAM(Double Port RAM), 以每行 数据为单位,采用乒乓结构进行数据 缓存,完成数据的无缝缓冲和整合。 在全色 FPGA 和多光谱 FPGA 内传输 延时均仅为一行数据的时间,极大增 强了图像输出实时性。乒乓存储即各 抽头奇数行数据向 DPRAModd 写入, 偶数行数据向 DPRAM<sub>Even</sub> 写入, 而写 DPRAM<sub>Odd</sub> 时读 DPRAM<sub>Even</sub>, 写 DPRAM<sub>Even</sub>时读 DPRAM<sub>Odd</sub>。此外还 要考虑每片 CCD 全色谱段 8 个抽头 输出像元是正序和倒序相结合的方式 (如图 1),因此奇数抽头输出的图像从 RAM 的低地址单元向高地址单元存 储,而偶数抽头输出的图像从 RAM 的高地址单元向低地址单元存储。各 DPRAM 均有独立的读写数据总线, 在写控制上, 其写地址和写信号共用 一套总线,以便各抽头图像数据的同 步写入;在读控制上,各 DPRAM 被

图 4 乒乓存储方式原理框图

Fig.4 Ping-pang storage block diagram

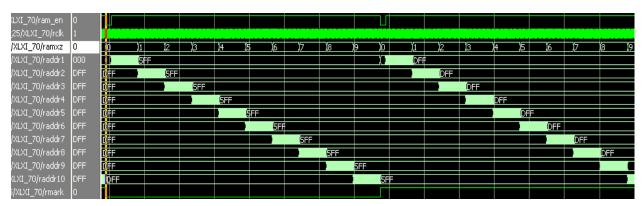

映射为统一地址编码的存储空间,各 RAM 地址空间的访问是通过读地址总线不变而读控制器对读数据总 线和读信号的切换来实现,具体如图 4 所示。在硬件上验证 FPGA 程序的正确性前,先在 ModelSim6.3SE 上进行充分的仿真验证,DPRAM 的读控制时序仿真波形如图 5 所示。

#### 2.4 图像数据高速传输及采集

LVDS(Low Voltage Differential Signaling)是一种高速低功耗低摆幅的差分信号技术,使用非常低的幅度信号(以+1.2 V 为基准约 350 mV 差分形式),通过一对差分 PCB (Printed Circuit Board)走线或平衡电缆传输数据<sup>[5]</sup>。LVDS 具有高速传输能力,理论极限速率为 1.923 Gbit/s;不论频率高低,LVDS 器件功耗低且恒

定不变;差分传输的特性决定了 LVDS 具有较强的抗共模噪声能力和较低的 EMI<sup>[9-10]</sup>。LVDS 的众多优势使其成为目前高速 I/O 接口的首选信号形式。因此本系统采用 LVDS 接口形式作为数字图像数据的传输格式,以此为数据的高速稳定传输提供保证。

图 5 DPRAM 控制时序仿真波形图

Fig.5 Time sequence simulation waveform of DPRAM control

SCSI (Small Computer System Interface)接口硬盘较传统 IDE(Integrated Drive Electronic)接口硬盘更适合高速数据存储,本系统采用带有 SCSI 控制器的 DVR Express CL-160 高速采集卡来模拟下位机实现高速图像数据的采集与存储,最终在 PC 机上显示采集到的图像。

#### 2.5 其他设计要点

为了保证采集到高质量的图像数据,就必须在系统设计时采用抗串扰设计、低噪声设计和电磁兼容设计等设计方法。除了选用低噪声器件、PCB 多层设计、3W 走线原则、模数地分离等常见措施,本系统还采取了以下措施来保证系统的性能:

- 1) 从视频信号处理单元到多光谱信号处理单元模拟视频信号采用同轴电缆传输,且源端和接收端阻抗 匹配,用以降低各通道间模拟信号的串扰和噪声;其余的模拟和数字信号线都采用特性阻抗控制技术和端 接技术避免信号自身的反射影响信号质量;

- 2) 对 CCD 多通道的电源供电、全色驱动器供电和多光谱驱动器供电均进行了隔离设计,并采取有效的去耦电容布线方法降低寄生电感,从而避免了由电源公共阻抗引起的串扰的产生;

- 3) 尽量缩短时钟走线长度,且其两侧有伴随地线;

- 4) 定义连接器信号时 LVDS 差分信号间插入地信号进行隔离降噪。

### 3 实验结果

为了验证系统是否满足设计要求,分别用 FPGA 内部的自校图形发生器产生的自校图形图像和滚筒推扫成像的图像对系统的实际传输速度和抗串扰、低噪声等性能进行了验证。图 6 和图 7 分别为测试实验接收到的自校图形图像和推扫成像图像,全色图像以 1.38 Gbit/s 的速率传输,多光谱图像以 880.7 Mbit/s 的速率传输。图像表明系统工作稳定可靠,无误码,图像清晰,实时传输稳定,且通道间无串扰现象,完全符合预期设计。

图 6 自校图形图像 Fig.6 Self-check figure image

Fig.7 Push-scanning image

### 4 结 论

本文设计的高速多光谱 TDICCD 图像数据传输系统为遥感相机图像数据传输系统的设计提供了一种新思路,该系统以 FPGA 作为主控制器,其实时性好、设计灵活且内部资源丰富,采用两级数据整合的方式,以其内嵌的 DPRAM 对图像数据进行无缝乒乓缓冲存储,采用 LVDS 接口对外输出。经实验测试系统总有效数据传输速率高达 8.66 Gbit/s。系统现已成功应用于某高速 TDICCD 相机成像系统的设计中,稳定可靠且方便移植,对其他 CCD 高速数据传输系统具有实际参考意义。

#### 参考文献:

- [1] 焦斌亮,王朝晖,林可祥,等. 星载多光谱 CCD 相机研究 [J]. 仪器仪表学报,2004, **25**(2): 146–151. JIAO Bin-liang, WANG Zhao-hui, LIN Ke-xiang, *et al.* A Multispectral CCD Camera for Satellite Use [J]. Chinese Journal of Scientific Instrument, 2004, **25**(2): 146–151.

- [2] 石俊霞,薛旭成,郭永飞. 卫星振动对 TDICCD 成像质量的影响及补偿方法[J]. 光电工程,2010,**37**(12): 11-16. SHI Jun-xia,XUE Xu-cheng,GUO Yong-fei. Effect of Satellite Vibration on Imaging Quality of TDICCD Camera and Compensation Method [J]. **Opto-Electronic Engineering**,2010,**37**(12): 11-16.

- [3] ZHU Hong-yin, XUE Xu-cheng, MA Tian-bo, *et al.* Correction of the non-uniformity for multi-TDICCD mosaic camera on FPGA [C]// **2010 International Conference on E-Product, E-Service and E-Entertainment**, Henan, China: IEEE, 2010: 3180–3183.

- [4] HAN Xiao-yan, THOMAS R L, FAVRO L D. High-Speed, High-Resolution Focal Plane Array Imaging System Final Report [R]. Detroit: Wayne State University, 2000.

- [5] 张达,徐抒岩. 高速多通道 CCD 信号并行处理系统 [J]. 吉林大学学报,2008,**26**(3): 281-286. ZHANG Da, XU Shu-yan. High-Speed Multi-Channel CCD Signal Parallel Processing System [J]. **Journal of Jilin University**, 2008, **26**(3): 281-286.

- [6] 马天波,郭永飞,李云飞. 科学级 TDICCD 相机的行频精度 [J]. 光学 精密工程,2010, **18**(9): 2028-2035. MA Tian-bo, GUO Yong-fei, LI Yun-fei. Precision of row frequency of scientific grade TDICCD camera [J]. **Optics and Precision Engineering**, 2010, **18**(9): 2028-2035.

- [7] 张鸿禹,刘爱东. 基于线阵 TDI-CCD 器件的扫描成像系统设计[J]. 光学与光电技术,2006,4(3): 49-52. ZHANG Hong-yu, LIU Ai-dong. Line-Scan Imaging System Based on the Linear Array TDI-CCD Camera [J]. Optics and Optoelectronic Technology, 2006,4(3): 49-52.

- [8] VirtexII Platform FPGAs: Complete Data Sheet [EB/OL]. (2007-11-5). http://www.xilinx.com.

- [9] 王胜,王新宇. LVDS 技术及其在高速系统中的应用 [J]. 遥测遥控, 2005, **26**(4): 41-46. WANG Sheng, WANG Xin-yu. LVDS and Its Application in High Speed System [J]. **Journal of Telemetry, Tracking, and Command**, 2005, **26**(4): 41-46.

- [10] 蒋冬初,李玉山. LVDS 在高速数字系统中的应用研究 [J]. 现代电子技术,2009(7): 147-150 JIANG Dong-chu, LI Yu-shan. Application of LVDS in High Speed Digital System [J]. **Modern Electronics Technique**,2009(7): 147-150.