http://dx.doi.org/10.1143/APEX.5.095601

## Improvements of Bilayer Ambipolar Organic Field-Effect Transistors Based on Pentacene and *N,N'*-Ditridecylperylene-3,4,9,10-tetracarboxylic Di-imide by Changing Growth Rate Method

Yongsheng Hu<sup>1,2</sup>, Nan Zhang<sup>1,2</sup>, Jie Lin<sup>1</sup>, Li Qin<sup>1</sup>, and Xingyuan Liu<sup>1\*</sup>

Received May 18, 2012; accepted August 8, 2012; published online August 28, 2012

The changing growth rate method is adopted for the first time to improve the performance of ambipolar organic field-effect transistors (OFETs). Pentacene and *N,N'*-ditridecylperylene-3,4,9,10-tetracarboxylic di-imide (PTCDI-C13) are chosen as p-type and n-type organic semiconductors, respectively. By modifying the dielectric surface with polystyrene, balanced carrier mobilities as high as 0.41 and 0.40 cm<sup>2</sup>·V<sup>-1</sup>·s<sup>-1</sup> for hole and electron, respectively, are achieved through such method, which are the highest values for air-stable ambipolar OFETs. Meanwhile, the devices show negligible hysteresis and air stability for more than one week. © 2012 The Japan Society of Applied Physics

mbipolar organic field-effect transistors (OFETs) have attracted wide attention in recent years for potential applications in fields such as organic complementary metal oxide semiconductor (CMOS) integrated circuits (ICs), organic light-emitting field-effect transistors (OLEFETs), and organic lasers. 1,2) Thus far, with the rapid advancement of organic semiconductor materials, however, the carrier mobilities and air stability of ambipolar OFETs are far from meeting practical use. Although devices with singlelayer architecture show carrier mobilities in the level of  $1 \text{ cm}^2 \cdot \text{V}^{-1} \cdot \text{s}^{-1}$ , they have poor air stability, especially for electron mobility. <sup>3,4)</sup> Devices with bilayer architecture usually have better air stability but poor carrier mobilities due to the restriction of the carrier mobility of each layer material. 1,5,6) The current state-of-the-art carrier mobilities of these devices, to our knowledge, are around  $0.1 \text{ cm}^2 \cdot \text{V}^{-1} \cdot \text{s}^{-1}$ .

For bilayer architecture devices, methods such as adjusting the thickness of each layer, controlling the substrate or annealing temperature, adopting various modifications and using asymmetrical electrodes that a proper changing growth rate was able to promote electron mobility and air stability for unipolar OFETs based on *N*, of ditridecylperylene-3,4,9,10-tetracarboxylic di-imide (PTCDI-C13), an n-type organic semiconductor material with relatively high electron mobility but poor air stability, we wonder whether this method will benefit ambipolar devices with bilayer architecture.

In this study, we demonstrate high-performance bottom-gate top-contact ambipolar OFETs based on pentacene and PTCDI-C13 working under ambient condition [RH: 40 ( $\pm 10$ ) %] by changing the growth rate of the PTCDI-C13 film. By further modifying the SiO<sub>2</sub> substrates with PS, the devices show good air stability and remarkable high and balanced carrier mobilities of 0.41 and 0.40 cm<sup>2</sup>·V<sup>-1</sup>·s<sup>-1</sup> for hole and electron, respectively, which are the highest for air-stable ambipolar devices to our knowledge.

Pentacene and PTCDI-C13 were purchased from Lumtech and Sigma-Aldrich, respectively. The substrate is heavily doped n-type silicon with 300 nm thermally oxidized SiO<sub>2</sub>. The surface of the substrate is either modified with PS (Sigma-

Aldrich,  $M_{\rm W}$  280,000) or not. We use anhydrous toluene as solvent for a solution of 10 mg/ml. After spin-coating at 2000 rpm for 30 s, the substrate is cured in vacuum at 120 °C for 1 h. The resulting thickness of PS is around 40 nm. Subsequently, 12 nm pentacene and 50 nm PTCDI-C13 are thermally evaporated onto the substrate at a base pressure of 1.5  $\times$  $10^{-4}$  Pa. The deposition rate of pentacene remains at 0.2 Å/s, while for PTCDI-C13, the deposition rate has three modes: Mode 1 is 0.2 Å/s; Mode 2 is 0.5 Å/s; Mode 3 is 0.05 Å/s for the first 5 nm and 0.2 Å/s for the subsequent 15 nm and 0.5 Å/s for the last 30 nm. When changing the growth rate, the samples are removed until the evaporation rate maintains stable. The substrate is kept at room temperature during the deposition. 50 nm Au is evaporated through a shadow mask with channel length and width of 200 and 4000 µm, respectively, which acts as the source and drain electrodes.

A quartz-crystal oscillator placed near the substrate is used to monitor the thickness and deposition rate of the field-effect transistors, which is calibrated *ex situ* using a surface profiler (Ambios XP-1). The electrical characteristics, including the voltage–current and capacitance measurements, are determined with Keithley 4200 SCS at room temperature under air ambient. The atomic force microscopy (AFM) tests are carried out with SPM-9700 (Shimadzu) under the phase mode. The carrier mobility is calculated using the following formula in the saturation regime:  $I_{\rm DS} = \mu C_{\rm i}(W/2L)(V_{\rm GS} - V_{\rm T})^2$ , where  $\mu$  is the field-effect mobility,  $C_{\rm i}$  is the gate dielectric capacitance density,  $V_{\rm T}$  is the threshold voltage, W and L are the channel width and length, respectively.

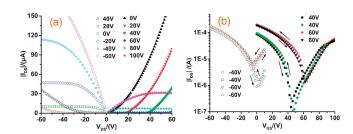

Figures 1(a)–1(b) compare the transfer characteristics of devices with the three growth modes. Due to the shifts of the threshold voltage, we choose those curves with approximately the same gate voltages when the minimum channel currents are reached to facilitate the comparison. Devices with mode 3 have greater electron on-current than those with modes 1 and 2, which indicates that less electrons are lost when transporting in the PTCDI-C13 layer grown by a different evaporation rate than those with a constant evaporation rate. For  $V_{\rm DS}=40\,\rm V$ , the calculated electron mobility in the saturation regime is  $0.10\,\rm cm^2\cdot V^{-1}\cdot s^{-1}$  ( $C_{\rm i}$  is  $\sim 11.5\,\rm nF\cdot cm^{-2}$ , which is tested using Keithley 4200 SCS at a frequency of  $100\,\rm kHz$  and averaged from several squares with different sizes), which is about  $100\,\rm and$   $70\%\,\rm higher$  than those with modes 1 and 2, respectively. The hole

<sup>&</sup>lt;sup>1</sup> State Key Laboratory of Luminescence and Applications, Changchun Institute of Optics, Fine Mechanics and Physics, Chinese Academy of Sciences, Changchun 130033, China

<sup>&</sup>lt;sup>2</sup> Graduate University of Chinese Academy of Sciences, Beijing 130039, China

<sup>\*</sup>E-mail address: liuxy@ciomp.ac.cn

Fig. 1. Transfer characteristics of devices with different growth modes: (a) electron accumulation region, (b) hole accumulation region. Transfer characteristics of devices with mode 3 under different test times: (c) electron accumulation region, (d) hole accumulation region.

**Table I.** Carrier mobilities  $(cm^2 \cdot V^{-1} \cdot s^{-1})$  and air stability of devices with different growth modes.

| Device process | Within 2h    |                    | 1 day later  |              | 7 days later |              |

|----------------|--------------|--------------------|--------------|--------------|--------------|--------------|

|                | $\mu_{ m p}$ | $\mu_{\mathrm{n}}$ | $\mu_{ m p}$ | $\mu_{ m n}$ | $\mu_{p}$    | $\mu_{ m n}$ |

| Mode 1         | 0.09         | 0.05               | 0.05         | 0.009        | 0.04         | _            |

| Mode 2         | 0.09         | 0.06               | 0.08         | 0.01         | 0.06         | _            |

| Mode 3         | 0.11         | 0.10               | 0.08         | 0.02         | 0.06         | 0.006        |

| Mode 3+PS      | 0.41         | 0.40               | 0.17         | 0.32         | 0.12         | 0.25         |

mobilities in the three modes are generally the same (see Table I for detail), which is  $0.1 \pm 0.01 \,\mathrm{cm}^2 \cdot \mathrm{V}^{-1} \cdot \mathrm{s}^{-1}$ . The gate voltage when the channel current becomes minimum is much higher than expected when  $V_{\rm DS}=40\,{\rm V}$ , and  $V_{\rm GS}$ even becomes positive when  $V_{\rm DS} = -40\,{\rm V}$ , which is different from most results in the literature. 12-14) However, the positive shift of V<sub>GS</sub> is also observed in the PTCDI-C8/ quaterrylene heteromolecular layer, which could be explained by the presence of intrinsic hole carriers in the holetransporting layer. 15) When intrinsic hole carriers exist, more positive  $V_{GS}$  is needed to deplete the hole carriers for the electron carrier accumulation and less negative  $V_{GS}$  for hole carrier accumulation. The presence of intrinsic hole carriers can be proved on the basis of the hole current when there is no gate bias ( $V_{GS} = 0 \text{ V}$ ). The origin of the intrinsic hole carriers could be the impurity of the material, structural defects, and involuntary doping by oxygen.

Large threshold voltage shifts during the electrical tests are observed for all the three growth modes. Figures 1(c)–1(d) are the transfer curves of devices with mode 3 for different test times. The threshold voltage shifts for electron and hole are more than 30 and 5 V, respectively, and the off-state current decreases as the test time increases. This suggests that there are large amounts of charge traps on the surface of SiO<sub>2</sub>.  $^{16,17}$  For  $V_{\rm DS}=\pm40\,\rm V$ , we calculate the electron and hole trap densities on the surface of SiO<sub>2</sub> to be  $4.3\times10^{11}$  and  $7.9\times10^{11}\,\rm cm^{-2}$ , respectively, using the following equation:  $^{18}$   $N_{\rm trap}=C_{\rm i}\times|V_{\rm T}-V_{\rm TO}|/q$ , in which  $C_{\rm i}$  is the gate dielectric capacitance density, q is the electronic charge,  $V_{\rm T}$  is the threshold voltage, and  $V_{\rm TO}$  is the turn-on voltage, which is defined as the gate voltage when  $dI_{\rm DS}/dV_{\rm GS}$  becomes positive [ $V_{\rm T}$  and  $V_{\rm TO}$  are tagged in

Figs. 1(c)–1(d)]. <sup>19)</sup> As for the air stability, devices with the three modes do not seem to be good. The electron mobility drops drastically after one day and almost no field effect is observed after one week of storage in air ambient. However, this is in accordance with the property of PTCDI-C13, since it fails easily in air ambient as we mentioned earlier. It is worth mentioning that devices with mode 3 still show electron mobility of 0.006 cm<sup>2</sup>·V<sup>-1</sup>·s<sup>-1</sup>, which proves that the changing growth rate method can promote the air stability of ambipolar devices to some degree.

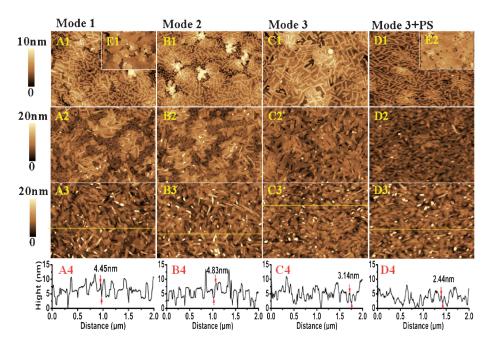

To further understand the influence of the growth rate, we investigate the morphology of the PTCDI-C13 films at different growth stages. Figure 2 shows the AFM topography images, in which A1-A3 are 5, 20, and 50 nm PTCDI-C13 films deposited on 12 nm pentacene under mode 1, while B1-B3 and C1-C3 are those under modes 2 and 3, respectively. The topography images show rod-like grains at the early stage (A1, B1, and C1). The average grain sizes of modes 1 and 2 are generally the same, around 120 nm, and those located at the gaps of pentacene films are even smaller. Although the grain gaps are wider for mode 3 (C1) than those in A1 and B1, the grain sizes are much larger, which are around 200 nm. As can be seen from C2, the grain gaps in C1 are well filled-in, and the grain sizes located at the gaps of pentacene films are much larger compared with those in A2 and B2. It is known that carriers are accumulated and transport in the first several molecular layers, thus, we think that the larger grain sizes at the early stage of mode 3 are attributed to the higher electron carrier mobility. In addition, the grain boundary depth (defined as the vertical distance from upper layer to inner layer along the gap of grain boundary) will reduce the physical adsorption of O<sub>2</sub>/ H<sub>2</sub>O molecules, <sup>11)</sup> which is known as the main device failure factor. Judging from A4, B4, and C4, the average grain boundary depth (averaged from measurements of the depths of more than 30 grain boundaries in the corresponding AFM cross-sectional height image) for A3, B3, and C3 are 4.45, 4.83, and 3.14 nm, respectively. We think this may be the reason why devices with mode 3 have better air stability than those with modes 1 and 2.

In order to diminish the shifts of threshold voltage and improve the carrier mobilities, we modify the substrate with PS and fabricate the device using mode 3. The AFM topography images are shown in Fig. 2. The pentacene film on PS (E2) is smoother than that on bare SiO<sub>2</sub>, and there are fewer gaps. The average grain sizes of PTCDI-C13 at the early stage (D1) are around 160 nm, which are smaller than those in C1 but with much narrower gaps. The average grain boundary depth is 2.44 nm. Figures 3(a)–3(b) show the output curve and transfer curve of the devices, respectively. The hole threshold voltage shifts negatively for more than 18 V compared with those without modification, and no threshold voltage shifts are observed during the electrical tests, which indicates a sharply reduced number of charge traps. The electron threshold voltage is also obviously reduced, from the typical value of 55 V before modification to 40 V after modification at  $V_{\rm DS} = 40$  V. The calculated electron and hole trap densities are now only  $2.4 \times 10^{11}$  and  $2.7 \times 10^{11} \,\mathrm{cm}^{-2}$ , respectively. Thus, modification of PS on SiO<sub>2</sub> can greatly reduce the charge surface traps, which is the key factor for the carrier mobility enhancement. For

Fig. 2. AFM topography  $(2 \times 1.4 \,\mu\text{m}^2)$  and cross-sectional height images of relevant films. A1–A3 are 5, 20, and 50 nm PTCDI-C13, respectively, grown on 12 nm pentacene under mode 1; B1–B3 and C1–C3 are those under modes 2 and 3, respectively; A4–D4 are corresponding cross-sectional height images in A3–D3; E1 and E2 are 12 nm pentacene on bare SiO<sub>2</sub> and PS modified SiO<sub>2</sub>, respectively.

**Fig. 3.** Characteristics of devices with PS modification of the substrate: (a) output curve; (b) transfer curve.

$V_{\rm DS} = \pm 60 \, \rm V$ , the hysteresis is negligible and the calculated ( $C_i$  is determined to be  $\sim 9.6 \,\mathrm{nF \cdot cm^{-2}}$  by Keithley 4200 SCS through the same way) hole and electron mobilities in the saturation regime are 0.41 and 0.40 cm<sup>2</sup>·V<sup>-1</sup>·s<sup>-1</sup>, respectively, which is the highest for air-stable ambipolar OFETs so far. Moreover, the air stability of the devices is also good. For devices stored in air ambient for one week, the electron mobility drops to less than half. It is worth mentioning that the hole mobility drops more drastically than the electron mobility, which is different from p-type OFETs based on pentacene. However, it agrees with what Choi's group<sup>6)</sup> observed in their ambipolar OFETs fabricated by the NCBD method. As they state, this may be because of the existence of the relatively larger hole traps than electron traps after the surface modification with PS. The detailed failure mechanism in this situation needs further investigation, which is beyond the scope of this paper.

In conclusion, air-stable ambipolar OFETs based on pentacene and PTCDI-C13 with high and balanced carrier mobilities are demonstrated, which is in favor of high-performance OLEFETs and organic lasers. The changing growth rate of the PTCDI-C13 layer and surface modification of the dielectric layer are proved to contribute to the considerable enhancement.

Acknowledgments This work was supported by the CAS Innovation Program, Jilin Province Science and Technology Research Project Nos. 20050108 and 20090346, and the National Science Foundation of China Nos. 51103144 and 61106057.

- R. Capelli, S. Toffanin, G. Generali, H. Usta, A. Facchetti, and M. Muccini: Nat. Mater. 9 (2010) 496.

- 2) J. Zaumseil and H. Sirringhaus: Chem. Rev. 107 (2007) 1296.

- J. L. Kan, Y. L. Chen, D. D. Qi, Y. Q. Liu, and J. Z. Jiang: Adv. Mater. 24 (2012) 1755.

- M. Irimia-Vladu, E. D. Glowacki, P. A. Troshin, G. Schwabegger, L. Leonat, D. K. Susarova, O. Krystal, M. Ullah, Y. Kanbur, M. A. Bodea, V. F. Razumov, H. Sitter, S. Bauer, and N. S. Sariciftci: Adv. Mater. 24 (2012) 375.

- 5) R. Ye, M. Baba, and K. Mori: Jpn. J. Appl. Phys. 44 (2005) L581.

- M. J. An, H. S. Seo, Y. Zhang, J. D. Oh, and J. H. Choi: Appl. Phys. Lett. 97 (2010) 023506.

- F. C. Chen and Y. J. Huang: Electrochem. Solid-State Lett. 12 (2009) H252.

- 8) R. Ye, M. Baba, K. Ohta, and K. Suzuki: Solid-State Electron. 54 (2010) 710.

- Y. Zhang, H. S. Seo, M. J. An, J. D. Oh, and J. H. Choi: J. Appl. Phys. 109 (2011) 084503.

- T. Sakanoue, E. Fujiwara, R. Yamada, and H. Tada: Chem. Lett. 34 (2005) 494.

- 11) Y. G. Wen, Y. Q. Liu, C. A. Di, Y. Wang, X. N. Sun, Y. L. Guo, J. Zheng, W. P. Wu, S. H. Ye, and G. Yu: Adv. Mater. 21 (2009) 1631.

- 12) C. Rost, S. Karg, and W. Riess: Appl. Phys. Lett. 85 (2004) 1613.

- 13) F. Dinelli, R. Capelli, M. A. Loi, M. Murgia, M. Muccini, A. Facchetti, and T. J. Marks: Adv. Mater. 18 (2006) 1416.

- 14) H. Shi, H. Wang, D. Song, H. Tian, Y. Geng, and D. Yan: Thin Solid Films 516 (2008) 3270.

- N. Hiroshiba, R. Hayakawa, T. Chikyow, K. Matsuishi, and Y. Wakayama: Org. Electron. 12 (2011) 1336.

- A. Salleo, F. Endicott, and R. A. Street: Appl. Phys. Lett. 86 (2005) 263505.

- 17) S. G. J. Mathijssen, M. Colle, H. Gomes, E. C. P. Smits, B. de Boer, I. McCulloch, P. A. Bobbert, and D. M. de Leeuw: Adv. Mater. 19 (2007) 2785

- 18) K. P. Pernstich, S. Haas, D. Oberhoff, C. Goldmann, D. J. Gundlach, B. Batlogg, A. N. Rashid, and G. Schitter: J. Appl. Phys. 96 (2004) 6431.

- T. J. Ha, P. Sonar, B. Cobb, and A. Dodabalapur: Org. Electron. 13 (2012)

136.