文章编号:1008-0570(2007)11-2-0206-03

# 利用 CPLD 实现对 TH58NVG1S3A 控制的研究

Research of Using CPLD to control TH58NVG1S3A

(1.中国科学院长春光学精密机械与物理研究所;2.中国科学院研究生院) 严海消 1,2 阮 锦 1 YAN HAIXIAO RUAN JIN

摘要:文中介绍了东芝公司的 2Gbits NAND 闪存芯片——TH58NVG1S3A 的基本结构, 阐述了如何利用 CPLD 芯片——ispLSI 1032E 对其进行控制, 并且给出了部分软件流程。

关键词:NAND 闪存;软件流程;CPLD

中图分类号:TN431.2 TN47 文献标识码:B

Abstract:In this paper, the basic architecture of the TOSHIBA 2Gbits NAND FLASH device--TH58NVG1S3A is introduced. Talk about how the CPLD device--ispLSI 1032E controls TH58NVG1S3A, and give some software flow.

Key words: NAND FLASH, software flow, CPLD

# 1 前言

闪存(又称 FLASH, 闪速存储器)是一种新兴的半导体存储器,是一种不挥发性存储器 NVM(Non- Volatile Memory)。它采用类似于 EPROM 的单管叠栅结构的存储单元,是新一代用电信号擦除的可编程 ROM; 既吸收了 EPROM 结构简单、编程可靠的优点,又具有 EEPROM 用隧道效应擦除的快捷特性,集成度可做得很高,因而在便携式数据存储和各种图像采集记录系统中得到了广泛的应用。其主要特点有:非易失性,可靠性高;功耗小;寿命长,可以在在线工作的情况下进行写入、读出和擦除操作,标准擦写次数可达 10 万次;密度大、成本低,具有很高的容量密度,价格也在不断降低;具有抗震动、抗冲击、温度适应范围宽等。正是由于闪存具有上述诸多优点,近年得到了快速而迅猛的发展。

全球闪速存储器的主要供应商有 AMD、Atmel、Fujistu、Hitachi、Hyundai、Intel、Micron、Mitsubishi、Samsung、SST、Sharp、Toshiba。由于各自技术架构的不同,分为几大阵营,因此闪速存储也按其采用技术的不同而分为几大类:

- \*NOR 技术——代表公司 Intel, 特点为擦除和写入慢、随机读快:

- \*NAND 技术——代表公司 Samsung、Toshiba, 特点为随机读写慢、以页为单位连续读写快;

- \*AND 技术——代表公司 Hitachi, 特点为低功耗, 价格高。

- \* 由 EEPROM 派生的闪速存储器。特点: 介于 NOR 与 EEPROM 之间。

存储器的发展具有容量更大、体积更小、功耗更低、价格更低的趋势,这在闪速存储器行业表现得淋漓尽致。随着半导体制造工艺的发展,主流闪速存储器厂家采用 90nm,甚至73nm 的制造工艺。

借助于先进工艺的优势,闪速存储器的容量可以更大: NOR 技术已经出现 512Mb 的器件, NAND 和 AND 技术已经有 32Gb 的器件。

芯片的封装尺寸更小: 从最初 DIP 封装, 到 PSOP、SSOP、

严海消: 硕士研究生

基金资助:中科院科研资助项目(X04Q01Z)

TSOP 封装, 再到 BGA 封装, 闪速存储器已经变得非常纤细小巧。

工作电压更低:从最初 12V 的编程电压,一步步下降到 5V、3.3V、2.7V、1.8V 单电压供电;符合国际上低功耗的潮流,更促进了便携式产品的发展。

位成本大幅度下降:采用 NOR 技术的 Intel 公司的 28F128J3 价格为 25 美元, NAND 技术和 AND 技术的闪速存储器已经突破 10MB/2 美元的价位,性价比极高。

本文中讨论的是采用 NAND 技术的 TH58NVG1S3A。

# 2 TH58NVG1S3A 芯片

TH58NVG1S3A 是 Toshiba 公司生产的一款闪存芯片。它的单片容量是 2Gbits, 采用的是 NAND 技术, 它可以在  $200\,\mu s$  内完成一页 2112 个字节的编程操作, 还可以在 2ms 内完成 128K 字节的擦除操作, 同时数据区内的数据能以 20MBps 的速度读出。

TH58NVG1S3A 大容量闪存芯片的 I/O 口既可以作为地址的输入端, 也可以作为数据的输入/输出端, 同时还可以作为指令的输入端。芯片上的写控制器能自动控制所有编程和擦除操作, 包括提供必要的重复脉冲、内部确认和数据空间等。

2.1 TH58NVG1S3A 芯片的性能参数

TH58NVG1S3A 的主要特点如下:

- \*采用 3.3V 电源;

- \* 芯片内部的存储单元阵列为(256+8192K) x8bits, 数据寄存器和缓冲存储器均为(2K+64) x8bits:

- \*具有指令/地址/数据复用的 I/O 口;

- \*由于采用可靠的 CMOS 移动门技术, 使得芯片最大可实现 100000 次编程/擦除操作, 该技术可以保证数据保存 10 年而不丢失。

表 1 TH58NVG1S3A 的编程和擦除时间

| 參  | 数    | 符号                | 最 短 | 典 型 | 最 长 | 单 位 |

|----|------|-------------------|-----|-----|-----|-----|

| 编和 | 星时间  | t <sub>PROG</sub> | _   | 200 | 700 | μs  |

| 块抱 | 察除时间 | t <sub>BERS</sub> | _   | 2   | 3   | ms  |

2.2 TH58NVG1S3A 芯片的主要引脚说明

TH58NVG1S3A 有 48 个引脚, 具体功能如下:

I/O0~I/O7: 数据输入输出口, I/O 口常用于指令和地址的输

入以及数据的输入/输出,其中数据在读的过程中输入。当芯片没有被选中或不能输出时,I/O口处于高阻态。

CLE:指令锁存端,用于激活指令到指令寄存器的路径,并在 WE 上升沿且 CLE 为高电平时将指令锁存。

ALE: 地址锁存端 用于激活地址到内部地址寄存器的路径,并在 WE 上升沿且 ALE 为高电平时,地址锁存。

CE:片选端 用于控制设备的选择。当设备忙时 CE 为高电平而被忽略,此时设备不能回到备用状态。

RE:读使能端,用于控制数据的连续输出,并将数据送到 I/O 总线。只有在 RE 的下降沿时,输出数据才有效,同时它还可以对内部数据地址进行累加。

WE:写使能控制端,用于控制 I/O 口的指令写入,同时,通过该端口可以在 WE 脉冲的上升沿将指令、地址和数据进行锁存。

WP:写保护端,通过 WP 端可在电源变换中进行写保护。当 WP 为低电平时,其内部高电平发生器将复位。

RY/BY\_N:就绪/忙输出, RY/BY\_N 的输出能够显示设备的操作状态。RY/BY\_N 处于低电平时, 表示有编程、擦除或随机读操作正在进行。操作完成后, RY/BY\_N 会自动返回高电平。由于该端是漏极开路输出, 所以即使当芯片没有被选中或输出被禁止时, 它也不会处于高阻态。

# 3 利用 CPLD 对 TH58NVG1S3A 控制的实现

本项目采用的 CPLD 是 LATTICE 公司的高密度在系统可编程逻辑器件 ISPLSI1032E, 这款 CPLD 有 84 脚和 100 脚两种封装形式,有 64 个 I/O 口供用户使用,内部集成 6000 门,有 192 个寄存器。能够满足设计需要。

#### 3.1 硬件连接

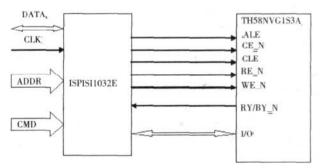

图 1 ISPLSI 1032E 控制 TH58NVG1S3A 硬件连接图

图 1 所示为 ISPLS1032E 控制 TH58NVG1S3A 芯片的主要信号连接情况。图中 ADDR、DATA、CMD 是系统与外部的接口信号,提供给用户使用; CLK 是输入到 CPLD 的时钟信号(频率为 20Mhz); 另外 ISPLS11032E 提供 6 根控制线和 8 根数据线以实现对 TH58NVG1S3A 的逻辑控制和数据交换,这些对用户是不透明的。ADDR 是提供给闪存的 29 位的地址输入线,可实现对闪存的 512M x8bits 单元寻址; CMD 为 3 位输入线表示对闪存的操作状态(读、写、擦除等); DATA 为双向 8 位数据线; RY/BY\_N 是 TH58NVG1S3A 的反馈信号, 示意操作过程是否结束; 其他信号是 TH58NVG1S3A 的控制信号。

### 3.2 软件设计

本文使用 VHDL 语言对 CPLD 进行编程。VHDL 语言具有很强的电路描述和建模能力,能从多个层次对数字系统进行建模和描述,使用 VHDL 语言对 CPLD 进行编程,可以将硬件工作软件化,从而大大简化了硬件设计任务,提高了设计效率和可靠

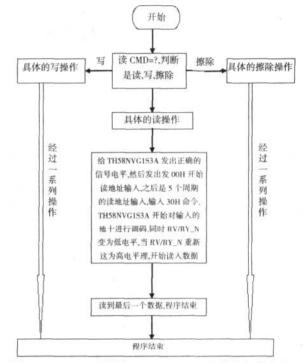

性,在语言方面具有很好的易读性;同时 VHDL 语言描述的系统是以并行方式工作的,大大提高了系统的运算速度;用 VHDL 语言进行电子系统设计的最大优点是使我们专致于功能的实现,而不需要对不影响功能的因素花费过多时间和精力,缩短了产品的开发时间。VHDL 是一种标准语言,不是针对某厂家的器件,而是针对所有可编程逻辑器件,因而具有普遍性,成为最常用的硬件描述语言。程序流程如图 2 所示。其中用 CMD=001 表示读闪存, CMD=010 表示对闪存进行写操作, CMD=100 表示对闪存进行块擦除。

图 2 ISPLSI1032E 控制 TH58NVG1S3A 芯片的程序流程

图 3 读操作仿真波形

TH58NVG1S3A 的读是按页执行的。读操作首先把 00H 命令写到指令寄存器作为读地址输入指令,一旦该指令被锁存,就不能在下页中写入读操作了,然后输入 5 个周期的地址数据到地址寄存器中进行地址译码,最后把 30H 写到指令寄存器作为读开始指令,但是并不是马上就能从闪存读出数据,直到将选定页中的 2112 字节数据存入数据寄存器后才能从闪存输出数据,系统可以通过分析 RY/BY\_N 脚的输出来判断数据转移是否完成。选定页中的 2112 字节数据能够在 25 µs 内被存入数据寄存器中,而存入数据寄存器的数据可以很快地被读出,数据通过周期为 50ns 的 RE 脉冲被连续输出至 I/O。

TH58NVG1S3A 的写操作也是按页进行的。首先输入连续数据输入指令80H,再输入5个周期的地址数据到地址寄存器中进行地址译码,之后在50ns的WE 周期上升沿将要写入的2112字节数据写入数据寄存器中,最后输入自动编程指令10H开始编程。可以通过查询RY/BY\_N 脚的输出来判断编程是否完成。编程完成后通过输入读状态寄存器70H来确定编程操作是否成功。虽然闪存的写操作是以页为单位的,但是

TH58NVG1S3A 可以将一页空间(2112 字节)分成 8 个部分(0-511, 512-1023, 1024-1535, 1536-2047, 2048-2063, 2064-2079, 2080-2095, 2096-2111)分别操作, 只是在进行写操作的时候, 把要进行写操作的部分写入需要的数据, 其他 7 个不需要进行写操作的部分必须写 "1"。

TH58NVG1S3A 的擦除操作是以块为单位进行的。块地址 装载将从一个块擦除指令 60H 开始, 之后是三个周期的块地址 输入, 然后输入擦除指令 D0H 开始擦除, 通过查询 R/B 来判断擦除操作是否完成。TH58NVG1S3A 内的状态寄存器可以确认编程和擦除操作是否成功完成。在写入指令(70H)到指令寄存器后, 读循环会把状态寄存器的内容在 RE 的下降沿输出到 I/O。而在新的指令到达前, 指令寄存器将保持读状态。

本文编程的读操作仿真波形如图 3, 写和擦除与读操作方式类似,不再赘述。

## 4 结束语

本文的创新点是成功使用 CPLD 控制 TOSHIBA 公司新推出的 2Gbits NAND FLASH 芯片 TH58NVG1S3A,完成了软硬件设计,使本系统相对于传统的存储方式来说更适用于非常恶劣的环境,有非常高的可靠性,能够承受强烈的震动,具有较低的功耗,灵活性高,控制方便,已经成功应用于某航天项目中,并产生了很好的效果。

#### 参考文献

[1]徐志军,徐光辉.CPLD/FPGA 的开发与应用. 北京:电子工业出版社,2002

[2]Toshiba 公司. TH58NVG1S3A Data Sheet.

[3]Lattice 公司. ISPLSI1032E Data Sheet.

[4]潘松 王国栋 VHDL 实用教程.成都 电子科技大学出版社, 2000

[5]吴松炎,余松煜,管云峰,基于单片机/CPLD的调压电路设计 [J],微计算机信息,2006

[6]李爱玲,张伯珩,基于 CPLD 的 CCD 相机图像信号模拟器的设计[J] 微计算机信息,2006

[7]王剑, 赵海燕 基于 CPLD 的控制器冗余设计[J] 微计算机信息 2005

[8]李春光 起月 ,王旭春 ,嵌入式微处理器与 FLASH 闪存的接口设计实现[J] ,微计算机信息 2006

作者简介: 严海消:1982-, 男, 汉族, 中国科学院长春光机与物理研究所 硕士研究生 机械电子工程 籍贯:河南, 研究方向: CCD 传感技术的应用;阮锦:1963-, 女, 中国科学院长春光机与物理研究所 研究员。

Biography: Yan Haixiao: 1982-, male, Han, Changchun Institute of Optics, Fine Mechanics and Physics, Chinese Academy of Sciences, master of mechanics& electronics engineering, HeNan, The application of CCD sensor; Ruan Jin: 1963-, female, Changchun Institute of Optics, Fine Mechanics and Physics, Chinese Academy of Sciences, Professor

(130033 长春 中国科学院长春光学精密机械与物理研究所) 严海消 阮锦

(100039 北京 中国科学院研究生院)严海消

(Changchun Institute of Optics, Fine Mechanics and Physics, Chinese Academy of Science, Changchun 130033, China) Yan Haixiao Ruan Jin

(Graduate School of Chinese Academy of Science, Beijing

100039, China)Yan Haixiao

通讯地址:(130033 长春 长春经济技术开发区东南湖大路 16 号 中国科学院长春光机与物理研究所空间光学部)李德志 转 严海消

(收稿日期:2007.8.13)(修稿日期:2007.10.20)

#### (上接第 198 页)

2)在突加负载的情况下, 系统能快速自动调节:

3)该系统实用性强,尤其适用于恒压供水、供气、供暖等恒值控制领域。

本文的创新点:将模糊 PID 控制与 DSP 相结合, 利用先进的 智能控制技术和 DSP 的高速数据处理能力的特点, 解决了传统的 PID 控制往往难以得到较理想的静、动态特性的问题, 从而提高了控制系统的智能化程度, 具有一定的推广价值。

项目经济效益:约20万元

### 参考文献

[1]诸静.模糊控制原理与应用(第二版). 北京:机械工业出版社, 2005

[2]刘建朋、刘建辉.基于 TMS320F240 的交流变频调速系统.[J]微计算机信息 2004 20(2):43-44

[3]刘和平.TMS320LF240XDSP结构原理及应用. 北京:北京航空航天大学出版社 2002

[4]刘金琨.先进 PID 控制 MATLAB 仿真(第二版). 北京:电子工业出版社,2004

[5]陶永华.新型 PID 控制及其应用(第二版). 北京:机械工业出版社 2002

作者简介:申昕(1973-), 男, 成都纺织高等专科学校讲师, 四川大学电子信息学院硕士研究生, 研究方向:智能控制、运动控制系统; 周新志(1969-), 男, 博士, 四川大学电子信息学院教授, 研究方向:智能控制、测控系统与技术。

Biography: Shen xin (1973-), Male, Lecturer, Master student. Research direction: Intelligent Control, control system of motion.

(610023 成都 成都纺织高等专科学校)申昕

(610064 四川 四川大学电子信息学院)申昕 周新志

(Chengdu textile institute, Chengdu 610023) Shen Xin (School of Electronics and information science,

University,Chengdu 610064,China)Shen Xin Zhou XinZhi 通讯地址:(610064 四川大学电子信息学院模式识别 05 级) 申昕

(收稿日期:2007.8.13)(修稿日期:2007.10.20)

# 书讯

《嵌入式系统应用精选200例》 110元/本(免邮资)汇至

《80C51宏汇编程序设计语言》 22 元 / 本( 免邮资) 汇至

地址:北京海淀区皂君庙 14 号院鑫雅苑 6 号楼 601 室 微计算机信息杂志收 邮编:100081