文章编号:1008-0570(2009)12-2-0167-02

# FPGA 在 IRIG-B 码源设计中的应用

FPGA is applied in the IRIG-B code Generator

(1.中国人民解放军 91245 部队:2.长春光学精密机械

与物理研究所;3.长春市农业机械研究所) 王智平 <sup>1</sup> 佟 刚 <sup>2</sup> 曹永刚 <sup>2</sup> 潘轶群 <sup>3</sup> WANG Zhi-ping TONG Gang CAO Yong-gang PAN Yi-qun

Wilvo Zhiping 10100 dang Cho long-gang 1710 lipqui

摘要: Cyclone 系列芯片是 Altera 公司推出的低价格、高容量的 FPGA,内置 M4K 存储块,最大 RAM 可达 288kb。IRIG-B 码是标准时间码格式之一,广泛的应用于靶场时间信息的传递和各系统的时间同步。利用 Cyclone 的内置 M4K 存储块,结合 MSP430 单片机设计的 IRIG-B 码时钟源,实现了系统的小型化、模块化。结果表明:该系统运行稳定,调试方便,克服了硬件电路复杂的缺点。

关键词: FPGA; IRIG-B码; 时间码中图分类号: TB114.2. 文献标识码: A

Abstract: Altera's low-cost high-content Cyclone series have M4K memory blocks, M4K memory blocks provide deeper and wider memory functions. Up to 288Kbits of RAM. IRIG-B code is one of the standard time code format, used for time information transfer and time synchronization between different ranges in the shooting range system. IRIG-B code generator base on M4K memory blocks and MSP430 achieved miniaturization and modularization. The results demonstrate that the system runs steadily, debug simply and hurdle the disadvantage of hardware circuit complexity.

Key words: FPGA; IRIG-B code; Time code

# 1 引言

时统设备是向导弹、航天试验各个参试设备提供标准时间 信号和标准频率信号的设备,只有各站的参试设备实现了时间统一,才能使整个导弹、航天试验任务得以顺利实施,因此,靶场时统设备是实施对导弹和航天器发射、测量和控制的重要设备之一。

IRIG-B 时间码(简称 B 码)以其优越的性能、简单易行的实现和使用方法成为时统设备首选的标志码型,但 IRIG-B 码时统设备存在电路复杂、集成度低、调试困难、成本高等缺点。为了解决上述问题,我们采用以 FPGA 为核心器件,结合 MSP430单片机和一些外围电路设计了一种新型的时统设备。测试结果表明,该系统具有性能稳定、可靠性高、便于调试等优点,有广泛的实际应用价值。

## 2 系统硬件设计

## 2.1 Cyclone 的结构特点

Cyclone 系列芯片是基于  $1.5V \cdot 0.13 \mu m$  的全铜层 SRAM 工艺。它具有生成时钟的锁相环以及 DDR SDR 和快速 RAM 存储器所需的专用双数据率(DDR)接口等。主要有以下特点:

- (1) 多电压接口, 支持 LVTTL,LVCMOS,SSTL-2,SSTL-3 和 LVDS 等 I/O 标准。

- (2)支持频率为 33MHz、66MHz,数据宽度为 32 位和 64 位的 PCI。

- (3)灵活的时钟管理,每个器件两个 PLL,可对时钟进行倍频、分频和相移。

- (4)低成本串行配置器件。

- (5)支持多种 IP 核。

王智平: 工程师

#### 2.2 IRIG-B 码原理

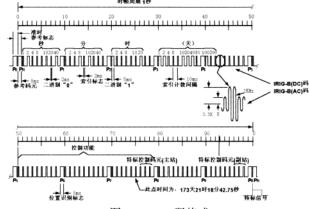

IRIG 是英文 Inter-Range Instrumentation Group 的缩写。IRIG 时间标准有两大类:一类是并行时间码格式;另一类是串行时间码,共有六种格式,即  $A \setminus B \setminus D \setminus E \setminus G \setminus H$ ,它们的主要差别是时间码的帧速率不同。B 码的主要特点是帧速率为每秒一帧;携带信息量大,适用于远距离传输,经译码后可获得  $1 \setminus 10 \setminus 100 \setminus 1 \times H$  的脉冲信号。B 码分为直流(DC)码和交流(AC)码两种,具有标准化接口,国际通用。格式如图  $1 \setminus H$  所示。

图 1 IRIG-B 码格式

#### 2.3 电路设计

由 B 码的特点可知,B 码产生是否正确,关键是在于能否产生各种信息的二进制编码,并实现并串转换,在一帧的适当位置插入帧同步码。将 1 秒帧周期分为 10 个功能块,每个功能块中包含 10 个码元,在前 5 个功能块中,将 BCD 码从个位到十位,由低到高依次排列,且在个位与十位之间有一个索引标志(当"0"处理)。在每一秒的开始都有一个参考码元,作为一帧开始的识别标志;每一个功能模块末尾都有一个位置标志。综合以上考

虑,B码源的设计电路分为直流(DC)码电路和交流(AC)码电路。

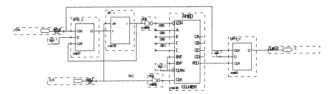

直流码电路采用 MSP430+FPGA 的方式,以 FPGA 为主。FPGA 分频链产生宽度(高电平)为 2ms,4ms,5ms 和 8ms,频率为100Hz 的脉冲信号,各种时标信号和控制信号。宽度为 2ms,4ms,5ms 和 8ms,频率为 100Hz 的脉冲信号经逻辑门控制电路产生出 B 码的三种基本编码形式。FPGA 内部逻辑根据时间信息控制 B 码这三种基本编码的输出,从而使时间信息按照 B 码的格式串行输出。FPGA 内部逻辑如图 2 所示。

图 2 直流码电路逻辑图

根据国军标,为了便于传递标准时间码,可用直流码对标准正弦波载频进行幅度调制。标准正弦波载频的频率与码元严格相关,一般为码元的十倍。同时,其正交过零点与所调制格式码元的前沿相符合,标准的调制比为 10:3。因此 B 码源设计应先生成直流码,并用直流码调制生成交流码。

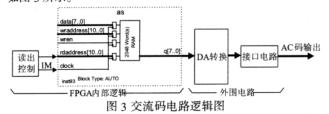

交流码是一对称的受幅度调制的正弦波信号,将量化的正弦波幅值固化在 FPGA 内的 RAM 中,正弦数据表的值按下面公式计算得出。

$$V_{data} = 127 + V_{p-p} \sin(2\pi \frac{n}{999})$$

N 取值从 0 到 999, 即每周期取 1000 个点, 交流码频率是 1KHz.因此 RAM 的读出频率是 1MHz。

$V_{pp}$  根据交流码调制比而改变。存储用多组不同  $V_{pp}$  计算得到的数据表  $V_{total}$  根据不同的调制比选择不同的地址读出数据表的值,可以实现交流码调制比的实时更改。FPGA 内部逻辑如图 3 所示。

## 3 系统软件设计

#### 3.1 系统初始化

在 IRIG-B 码源设计中,CPU 采用的是

TI 公司 MSP430。MSP430 是 16 位高性能系列单片机,其高效 16 位精简指令结构可以确保任务的快速执行,大多数指令可以在一个时钟周期内完成,且具有高级语言编程的能力。 MSP430 采用 C 语言进行编程开发,这里只介绍系统初始化的程序,工作是建立程序运行的环境,如中断设置、系统的工作频率的设置、定时器的设置、看门狗的设置等。下面是 MSP430 的初始化程序:

```

void InitSys(void)

{

BCSCTL1&=~XT2OFF; //打开 XT2 振荡器

BCSCTL2 = SELM_2+SELS+DIVS_3;

TACTL=TASSEL1+TACLR: // 时钟源 SMCLK.

```

#### 定时器清零

TACTL |= MC1; //连续记数模式

ADC12CTL0 &= ~(ENC); //修改 ADC12 寄存器的值

ADC12CTL1 |= SHP; //采样脉冲由采样定时器产生

ADC12CTL0 |= ADC12ON; //A/D 转换

ADC12CTL0 |= REFON+REF2\_5V; //内部参考电压 2.5v

ADC12CTL0 |= MSC+SHT0\_4;

> ADC12MCTL6 = SREF\_1+INCH\_6; ADC12MCTL7 = SREF\_1+INCH\_7;

#### 3.2 程序流程

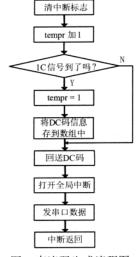

图 4 所示为直流码生成程序流程图。程序主要包括 1C 中断、100C 中断、并口数据发送、串口数据发送等。

## 4 结论

高准确度和稳定度的 IRIG-B 码时钟源是获得各种准确数据、实时精密测量和控制飞行目标的基础。随着科学技术的发展,对 IRIG-B 码源的功能、体积、精度、可靠性等技术指标提出越来越高的要求。设计结果表明,以 FPGA 为核心的 IRIG-B 码源数据处理灵活方便,而且外围硬件电路简单,可以提高 IRIG-B 码信息的可靠性及适应能力.保证系统精度。

创新观点:本文根据 Cyclone 系列 FPGA 内置 M4K 存储块, 提出了将交流码正弦波幅值存储在 FPGA 内部 RAM 中,以简化 电路设计。实验证明此种设计方式灵活方便,满足系统要求。

图 4 直流码生成流程图

#### 参考文献

[1]徐光辉等.基于 FPGA 的嵌入式开发与应用.电子工业出版社, 2006.

[2]童宝润.时间统一系统.国防工业出版社,2003.

[3]杨蕾,胡永辉.CPLD 技术及其在现代时统中的应用.时间频率 学报.2003:26(1):40~47.

[4]崔明,佟刚等.基于 MSP430 的纸张耐压强度检测系统.微计算 机信息.2007.10-2:4~5.

作者简介:王智平(1977.8-),男,主要从事光电测量方面的研究; 佟刚(1978.6-),男,主要研究方向为光电精密跟踪测量技术。

(下转第 12 页)

由仿真的带通滤波器的频率响应曲线可得到滤波器的性能指标参数,并与根据传输函数()理论计算的滤波器性能参数的对照表如表 1 所示。比较可见仿真的结果和理论推倒出的结果吻合的比较好; 因为开关电容滤波器的性能参数主要由开关频率和电容比决定, 受工艺参数影响较少可以实现精确的滤波器特性,设计实现比较简单。

## 4 结论

本文设计了一个用于 RDS 信号多径检测的二阶带通开关电容滤波器。详细分析了开关电容滤波器的工作原理和设计过程;成功设计实现了一个高精度、高线性度的开关电容滤波器。该滤波器模块在一款 RDS 解调电路中的得到了实现验证,功能模块正常,目前该芯片正在实现批量生产,预计经济效益可达100万元。

本文创新点:提出了一种开关电容带通滤波器的设计方法和仿真方法,利用该方法成功设计实现了一个应用于 RDS 信号多径检测的开关电容带通滤波器,并成功应用在一款 RDS 解调电路中。

#### 参考文献

[1]Tech.3244-E: Specification of The Radio Data System RDS for VHF/FM Sound Broadcasting, EBU Document, 1984.

[2]张春艳,严利民,宁伟超.一种 Sigma-Delta 调制器的电路实现. 微计算机信息,2007.6-2:0279-03

[3]David A. Johns and Ken Martin. Analog Integrated Circuit Design 北京:机械工业出版社,2005 263-312

[4]Richard E. Vallee and Ezz I. EI-Masry, "A Very High-Frequency CMOS Complementary Folded Cascode Amplifier" IEEE J. Solid-State Circuit, vol. 29, No.2, Feb. 1994

[5]A. Shankar, J. Silva-Martinez, and E.Sanchez-Sinencio, "A Low Voltage Operational Transconductance Amplifier Using Common Model Feedforward for High Frequency Switched capacitor circuits" IEEE, Circuits and Systems, Vol. 1.6–9, May. 2001

[6]侯卫卫,冯全源。一种高性能单位增益放大器。微计算机信息, 2007.02-2:0292-02

[7]Alan Hastings. The Art of Analog Layout (Second Edition) 北京: 清华大学出版社 2004

[8]Phillip E. Allen, Douglas R. Holberg. CMOS Analog Circuit Design (second Edition) 北京:电子工业出版社,2002 532-544

作者简介:孙金中(1983-),男,安徽省亳州人,中国科学院微电子所在读直博研究生,专业微电子学与固体电子学,主要研究方向大规模数模混合集成电路研究与产品开发;冯炳军(1969-),男,杭州中科微电子有限公司,副研究员,研究生导师,主要研究方向数模混合集成电路与系统设计。

**Biography:**SUN Jin-zhong (1983 – ), male, Anhui Province, candidate for doctor degree on Microelectronics and Solid State Electronics, Institute of Microelectronics of Chinese Academy of Science, major in digital and analog integrate circuit research and production design.

(100080 北京 中国科学院微电子研究所) 孙金中 叶甜春 (310053 杭州 杭州中科微电子有限公司) 冯炳军

通讯地址:(310053 杭州市滨江区江南大道 3850 号创新大厦 10F) 孙金中

(收稿日期:2009.02.12)(修稿日期:2009.05.12)

#### (上接第 161 页)

## 4 结束语

在谐波检测仪设计中,采用 RS485 总线技术和 Modbus 协议,实现了下位机与上位机之间的通信。采用高速 DSP 芯片,实现了 FFT,检测到了非常准确的各次谐波。试验结果表明:该谐波检测仪性能稳定,测量精度高、通信速度较快,符合中华人民共和国《电能质量 公用电网谐波》对 B 级谐波测量仪器的要求:谐波幅度大于基波幅度 3%时,谐波测量误差小于 5%谐波幅度;谐波幅度大于基波幅度 3%时,谐波测量误差小于 0.05%基波幅度。通过应用,该设计取得良好的经济效益和社会效益。

本文作者创新点:设计了基于 DSP 技术的谐波检测仪,并将 RS485 总线技术和 Modbus 通信协议结合,实现了谐波检测仪与由 VB 设计的上位机监控软件的通信,满足了谐波检测系统的通信要求,并取得了良好的效果。

项目经济效益(50万元)。

#### 参考文献

[1]陈其松,陈孝威等.电力系统谐波检测与抑制[J].微计算机信息, 2007.8-1: 258-260.

[2]郭巍,陈友龙. 基于 MATLAB 的小波变换在谐波检测上的仿真方法 [J]. 微计算机信息,2006,8-1:288-289:

[3]石东海.单片机数据通信技术从入门到精通[M].西安:西安电子科技大学出版社,2002.

[4]陈树广,武君胜. RS485 总线在智能抄表系统中的应用研究[J]. 微计算机信息,2008,5-1: 148-150.

作者简介:王飞(1977-),男,汉族,讲师,广东佛山人,研究方向为电力电子与电力拖动;林梅金(1981-)女,汉族,讲师,广东佛山人,研究方向为电器智能化技术; 杨兆华(1964-),男,汉族,教授,广东佛山人,研究方向为电力电子与电力拖动。

**Biography:** WANG Fei(1977-), Male, the Han nationality, Master, GuangDong, Foshan University, Research area: Power Electronics and Electric Traction.

(528000 广东佛山 佛山科学技术学院) 王 飞 林梅金 杨兆华 (Foshan University, Foshan, 528000, China) WANG Fei LI Mei-jin YANG Zhao-hua

通讯地址:(528000 广东佛山江湾一路 18 号佛山科学技术学院 机电学院) 王 飞

(收稿日期:2009.02.07)(修稿日期:2009.05.07)

## (上接第 168 页)

**Biography:** WANG Zhi-ping (1977 – ), male (Han nationality), Unit 91245 of the Chinese People's Liberation Army. Studying on technology of photo-electronic measure.

(125000 中国人民解放军 91245 部队) 王智平

(130033 长春 长春光学精密机械与物理研究所) 佟 刚 曹永刚 (130021 长春 长春市农业机械研究所) 潘轶群

(Unit 91245 of the Chinese People's Liberation Army,125000, China) WANG Zhi-ping

(Changchun Institute of Optics, Fine Mechanics and Physics, Changchun, 130033, China) TONG Gang CAO Yong-gang (Changchun Institute of agriculture machine, Changchun, 130021, China) PANG Yi-qun

通讯地址:(130033 吉林长春东南湖大路 3888 号 长春光学精密 机械与物理研究所光电测控部) 佟 刚

(收稿日期:2009.02.16)(修稿日期:2009.05.16)